# MITSUBISHI 16-BIT SINGLE-CHIP MICROCOMPUTER M16C FAMILY

#### Keep safety first in your circuit designs!

• Mitsubishi Electric Corporation puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage. Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of non-flammable material or (iii) prevention against any malfunction or mishap.

#### Notes regarding these materials

- These materials are intended as a reference to assist our customers in the selection of the Mitsubishi semiconductor product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Mitsubishi Electric Corporation or a third party.

- Mitsubishi Electric Corporation assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts or circuit application examples contained in these materials.

- All information contained in these materials, including product data, diagrams and charts, represent information on products at the time of publication of these materials, and are subject to change by Mitsubishi Electric Corporation without notice due to product improvements or other reasons. It is therefore recommended that customers contact Mitsubishi Electric Corporation or an authorized Mitsubishi Semiconductor product distributor for the latest product information before purchasing a product listed herein.

- The information described here may contain technical inaccuracies or typographical errors. Mitsubishi Electric Corporation assumes no responsibility for any damage, liability or other loss rising from these inaccuracies or errors.

- Mitsubishi Electric Corporation semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Mitsubishi Electric Corporation or an authorized Mitsubishi Semiconductor product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.

- The prior written approval of Mitsubishi Electric Corporation is necessary to reprint or reproduce in whole or in part these materials.

- If these products or technologies are subject to the Japanese export control

restrictions, they must be exported under a license from the Japanese government

and cannot be imported into a country other than the approved destination.

Any diversion or reexport contrary to the export control laws and regulations of

Japan and/or the country of destination is prohibited.

- Please contact Mitsubishi Electric Corporation or an authorized Mitsubishi Semiconductor product distributor for further details on these materials or the products contained therein.

#### **Preface**

This manual describes the basic knowledge of application program development for the M16C/80 series of Mitsubishi CMOS 16-bit microcomputers. The programming language used in this manual is the assembly language.

If you are using the M16C/80 series for the first time, refer to Chapter 1, "Overview of M16C/80 Series". If you want to know the CPU architecture and instructions, refer to Chapter 2, "CPU Programming Model" or if you want to know the directive commands of the assembler, refer to Chapter 3, "Functions of Assembler". If you want to know practical techniques, refer to Chapter 4, "Programming Style".

The instruction set of the M16C/80 series is detailed in "M16C/80 Series Software Manual". Refer to this manual when the knowledge of the instruction set is required.

For information about the hardware of each type of microcomputer in the M16C/80 series, refer to the user's manual supplied with your microcomputer. For details about the development support tools, refer to the user's manual of each tool.

| Chapter 1  | Overview of M16C/80 Series | 1                    |

|------------|----------------------------|----------------------|

| Chapter 2  | CPU Programming Model      | 2                    |

| Chapter 3  | Functions of Assembler     | 3                    |

| Chapter 4  | Programming Style          | <u>4</u> ,           |

| Appendix . |                            | <mark>ppendix</mark> |

#### Guide to Using This Manual

This manual is an assembly language programming manual for the M16C/80 series. This manual can be used in common for all types of microcomputers built the M16C/80 series CPU core.

This manual is written assuming that the reader has a basic knowledge of electrical circuits, logic circuits, and microcomputers.

This manual consists of four chapters. The following provides a brief guide to the desired chapters and sections.

- To see the overview and features of the M16C/80 series

- -> Chapter 1 Overview of M16C/80 Series

- To understand the address space, register structure, and addressing and other knowledge required for programming

- -> Chapter 2 CPU Programming Model

- To know the functions of instructions, the method for writing instructions, and the usable addressing modes

- -> Chapter 2 CPU Programming Model, 2.6 Instruction Set

- To know how to use interrupts

- -> Chapter 2 CPU Programming Model, 2.7 Outline of Interrupt

- -> Chapter 4 Programming Style, 4.3 Setting when using Interrupts

- To check the functions of and the method for writing directive commands

- -> Chapter 3 Functions of Assembler, 3.2 Method for Writing Source Program

- To know the M16C/80 series' programming techniques

- -> Chapter 4 Programming Style, 4.5 A Little Tips...(Programing technique)

- To know the M16C/80 series' development procedures

- -> Appendix Command input form and command parameters in AS308 system

### M16C Family-related document list

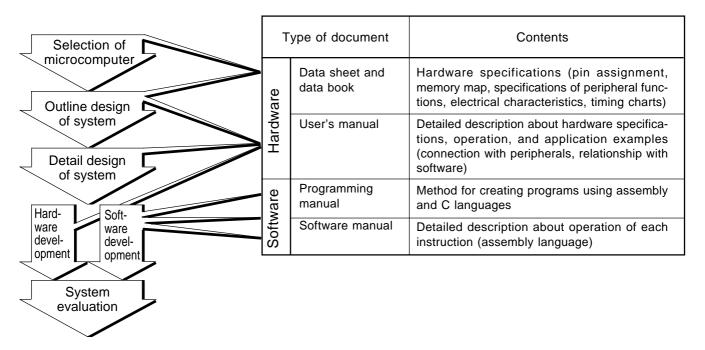

# Usages (Microcomputer development flow)

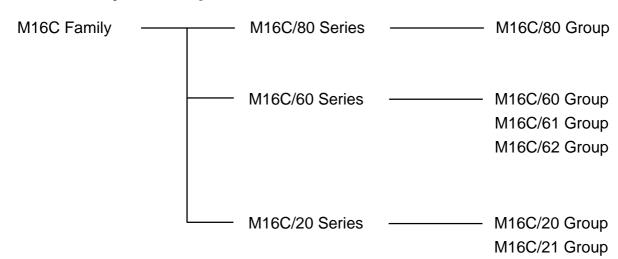

### M16C Family Line-up

# **Table of contents**

# **Chapter 1 Overview of M16C/80 Series**

| 1.1 Features of M16C/80 Series                        |    |

|-------------------------------------------------------|----|

| 1.2 Outline of M16C/80 Group                          | 3  |

| Chapter 2 CPU Programming Model                       |    |

| 2.1 Address Space                                     | 8  |

| 2.1.1 Operation Modes and Memory Mapping              | 8  |

| 2.1.2 SFR Area                                        | 10 |

| 2.1.3 Fixed Vector Area                               |    |

| 2.2 Register Set                                      | 16 |

| 2.3 Data Types                                        | 22 |

| Figure 2.3.1 Integer data                             | 22 |

| Figure 2.3.2 Decimal data                             | 22 |

| Figure 2.3.3 String data                              | 23 |

| Figure 2.3.4 Specification of register bits           | 23 |

| Figure 2.3.5 Specification of memory bits             | 23 |

| 2.4 Data Arrangement                                  | 24 |

| 2.5 Addressing Modes                                  | 25 |

| 2.5.1 General Instruction Addressing                  | 27 |

| 2.5.2 Indirect instruction Addressing                 | 35 |

| 2.5.3 Special Instruction Addressing                  | 38 |

| 2.5.4 Bit Instruction Addressing                      | 40 |

| 2.6 Instruction Set                                   | 45 |

| 2.6.1 Instruction Description                         | 46 |

| 2.6.2 Instruction List                                | 48 |

| 2.6.3 Transfer Instructions                           | 68 |

| 2.6.4 Arithmetic Instructions                         | 72 |

| 2.6.5 Branch Instructions                             | 80 |

| 2.6.6 Bit Instructions                                |    |

| 2.6.7 Sign-extension instruction                      | 87 |

| 2.6.8 Index instruction                               |    |

| 2.6.9 High-level language and OS support instructions | 90 |

| 2.7 Outline of Interrupt                              |    |

| 2.7.1 Interrupt Sources and Vector addresses          |    |

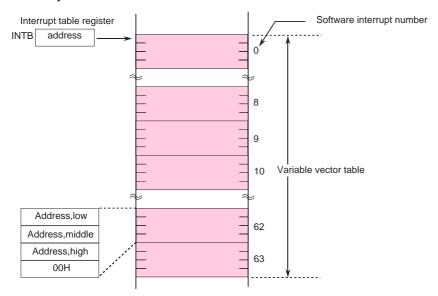

| 2.7.2 Variable vector table                                                      | 98        |

|----------------------------------------------------------------------------------|-----------|

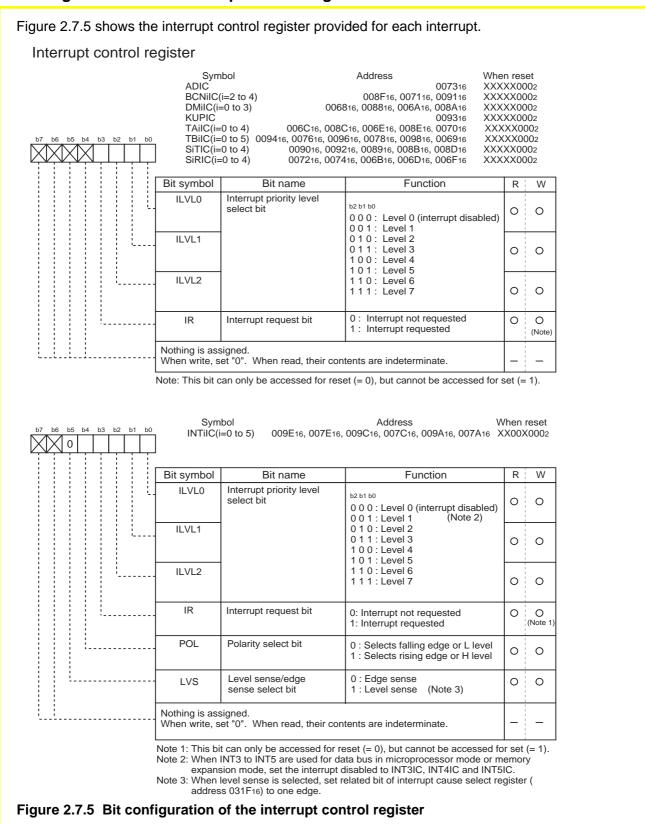

| 2.7.3 Interrupt generation conditions and interrupt control register bit configu | uration99 |

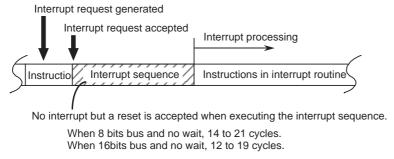

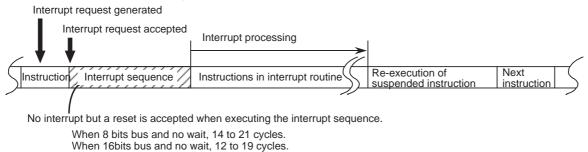

| 2.7.4 Interrupt acceptance timing and sequence                                   | 101       |

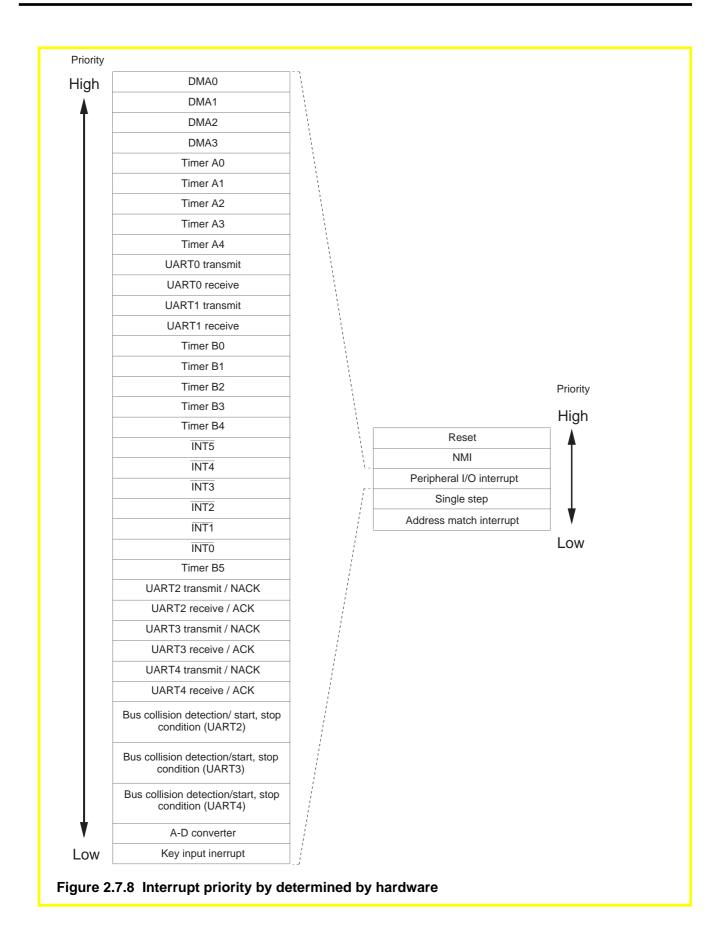

| 2.7.5 Interrupt priority                                                         | 103       |

| Chapter 3 Functions of Assembler                                                 |           |

| 3.1 Outline of AS308 System                                                      | 106       |

| 3.2 Method for Writing Source Program                                            | 109       |

| 3.2.1 Basic Rules                                                                | 109       |

| 3.2.2 Address Control                                                            | 117       |

| 3.2.3 Directive Commands                                                         | 124       |

| 3.2.4 Macro Functions                                                            |           |

| 3.2.5 Differences with M16C/60                                                   | 138       |

| Chapter 4 Programming Style                                                      |           |

| 4.1 Hardware Definition                                                          | 144       |

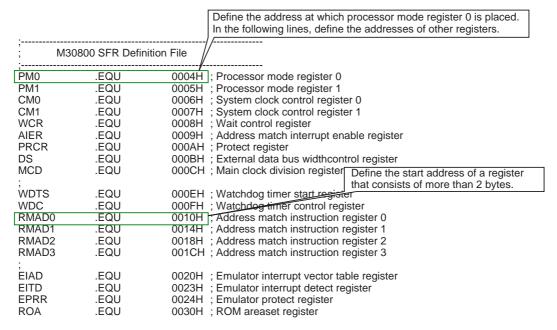

| 4.1.1 Defining SFR Area                                                          | 144       |

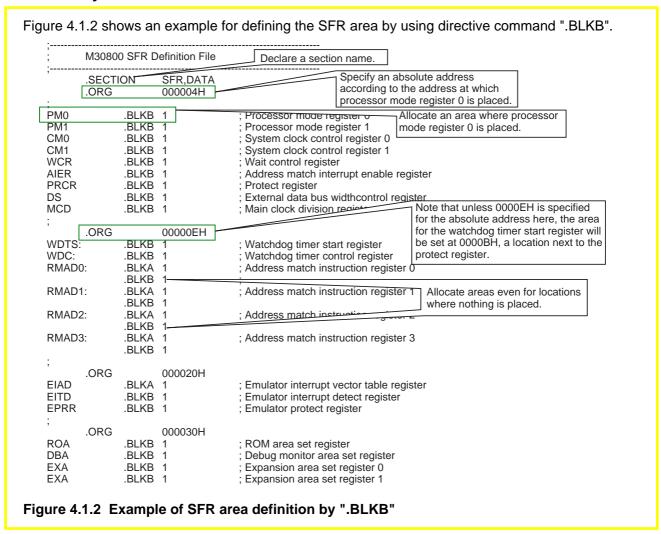

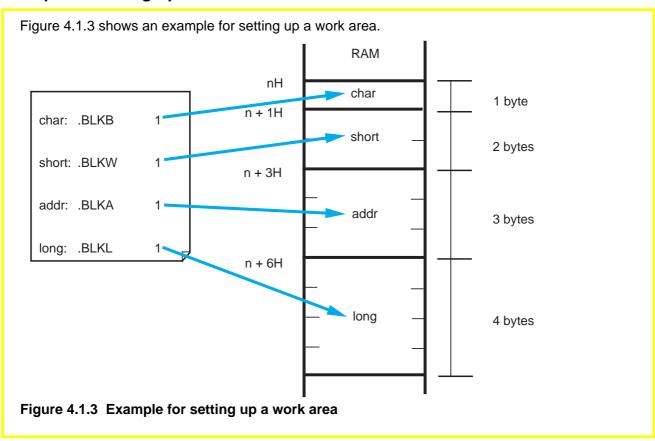

| 4.1.2 Allocating RAM Data Area                                                   | 147       |

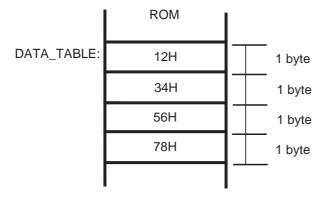

| 4.1.3 Allocating ROM Data Area                                                   | 148       |

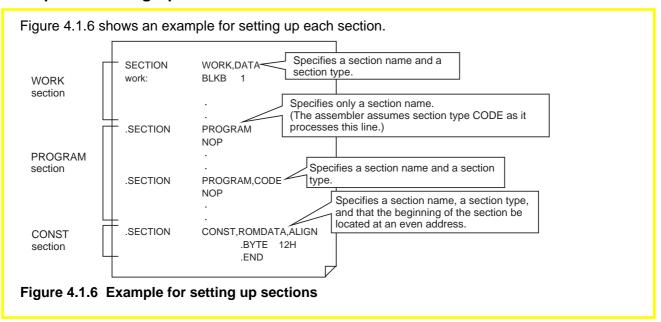

| 4.1.4 Defining a Section                                                         | 149       |

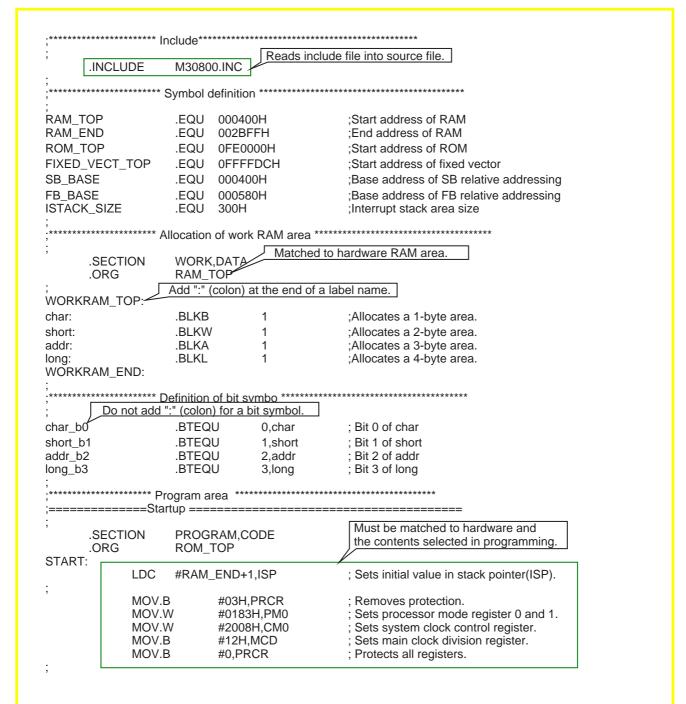

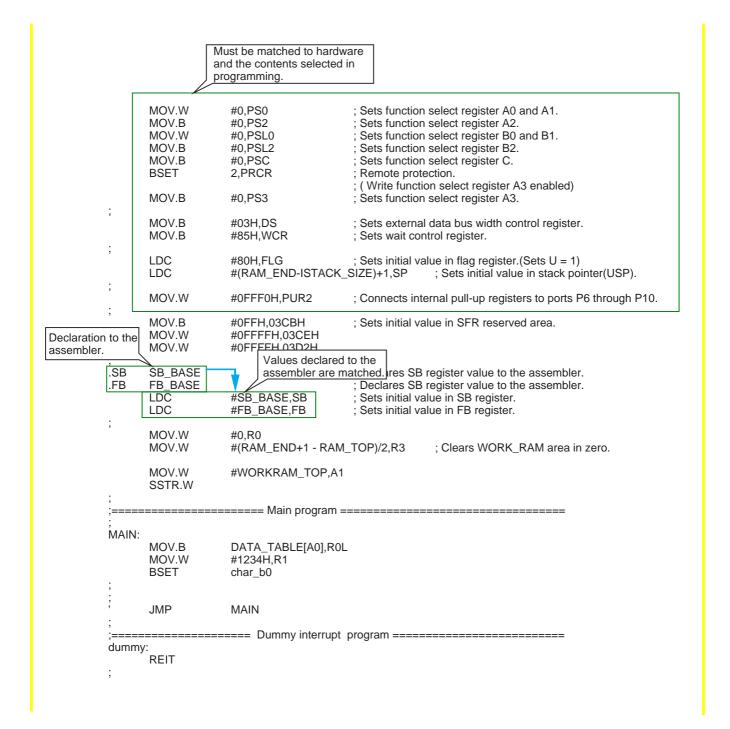

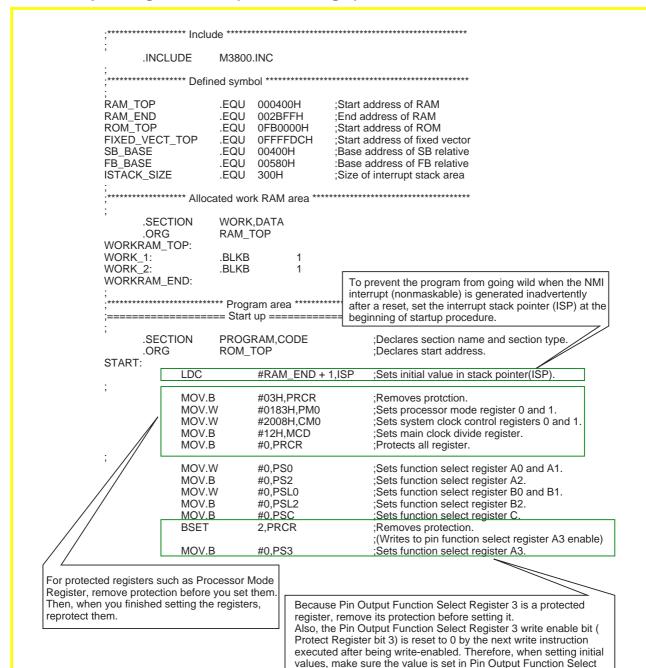

| 4.1.5 Sample Program List 1 (Initial Setting 1)                                  | 151       |

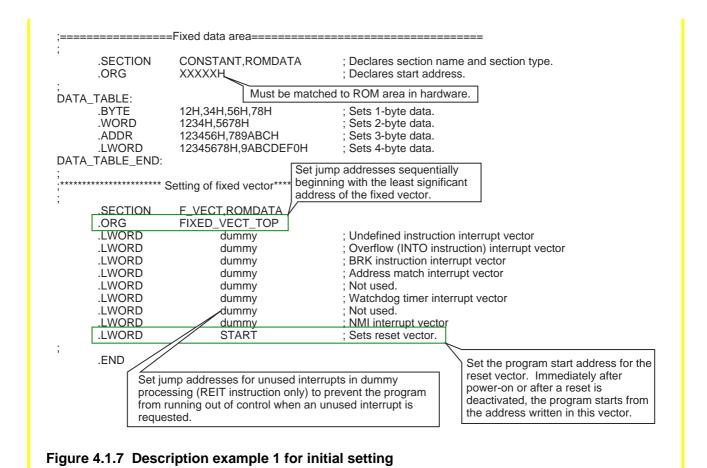

| 4.2 Initial Setting the CPU                                                      | 154       |

| 4.2.1 Setting CPU Internal Registers                                             | 154       |

| 4.2.2 Setting Stack Pointer                                                      | 155       |

| 4.2.3 Setting Base Registers (SB, FB)                                            | 155       |

| 4.2.4 Setting fixed interrupt vector (reset vector)                              | 156       |

| 4.2.5 Setting internal peripheral functions                                      | 156       |

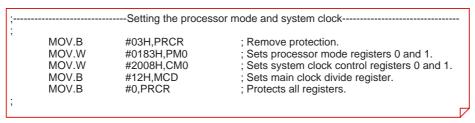

| 4.2.6 Sample Program List 2 (Initial Setting 2)                                  | 161       |

| 4.3 Setting when using Interrupts                                                | 164       |

| 4.3.1 Setting Interrupt Table Register(INTB)                                     | 164       |

| 4.3.2 Setting Variable/Fixed Vectors                                             | 165       |

| 4.3.3 Setting Interrupt Control Register                                         |           |

| 4.3.4 Enabling Interrupt Enable Flag( I flag)                                    |           |

| 4.3.5 Saving and Restoring Registers in Interrupt Handler Routine                |           |

| 4.3.6 Sample Program List 3 (Using interrupts)                                   |           |

| 4.3.7 ISP and USP                                                                | 174       |

| 4.3.8    | Multiple Interrupts                                     | 177 |

|----------|---------------------------------------------------------|-----|

| 4.3.9    | High-speed interrupts                                   | 178 |

| 4.4 Divi | ding Source File                                        | 182 |

| 4.4.1    | Concept of Sections                                     | 182 |

| 4.4.2    | Example of program description in divided files         | 184 |

| 4.4.3    | Using library files                                     | 190 |

| 4.5 A Li | ttle Tips(Programing technique)                         | 192 |

| 4.5.1    | Setup Values of SB and FB Registers                     | 192 |

| 4.5.2    | Specifying ROM/RAM data alignments                      | 196 |

| 4.5.3    | Setting stack pointer                                   | 198 |

| 4.5.4    | Using special pages                                     | 201 |

| 4.5.5    | Example for using software interrupt (INTO instruction) | 203 |

| 4.5.6    | Software runway prevention                              | 205 |

| 4.5.7    | Method for using the "-LOC" option                      | 209 |

| 4.6 Star | ndard processing program                                | 210 |

|          |                                                         |     |

|          |                                                         |     |

| nnor     | div Command input form and                              |     |

# Appendix Command input form and command parameters in AS308 system

| Apper                      | Generating Object Files    | Appendix A |

|----------------------------|----------------------------|------------|

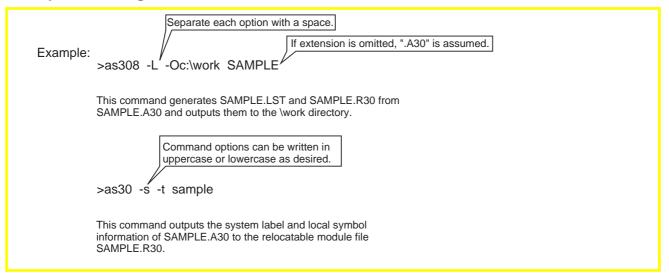

| Арре                       | A-1 Assembling (as308)     | Appendix i |

| Арре                       | A-2 Linking(In308)         | Appendix / |

| nguage File (Imc308) Appen | A-3 Generating Machine Lar | Appendix A |

# **Table of contents for figure**

# **Chapter 1 Overview of M16C/80 Series**

| 1.1 Features   | of M16C/80 Series ———————————————————————————————————— |    |

|----------------|--------------------------------------------------------|----|

| 1.2 Outline of | f M16C/80 Group ————————————————————————————————————   |    |

|                | 1 Block diagram of the M16C/80 group                   |    |

| Chapter 2      | 2 CPU Programming Model                                |    |

| 2.1 Address    | Space ————                                             |    |

| Figure 2.1.1   | 1 Address space                                        | 8  |

| Figure 2.1.2   | 2 Operation modes and memory mapping                   | 9  |

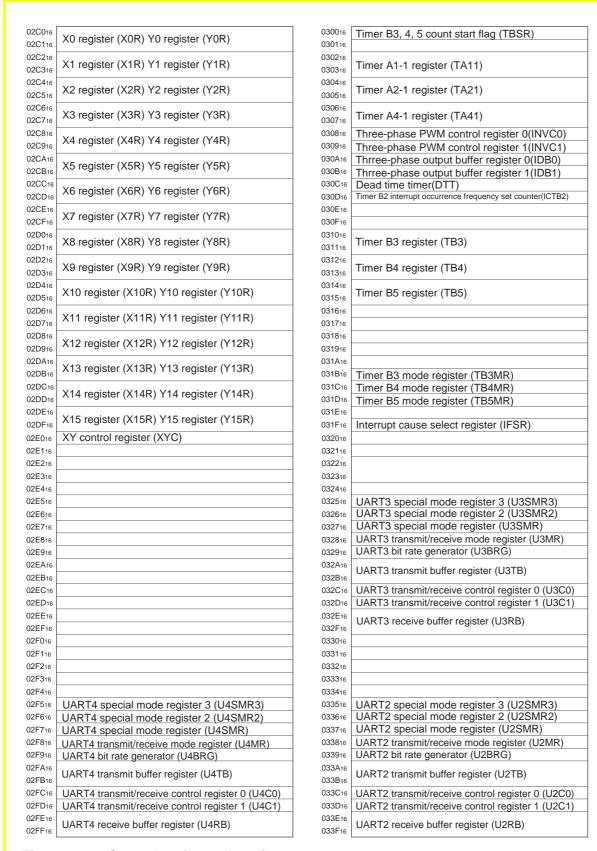

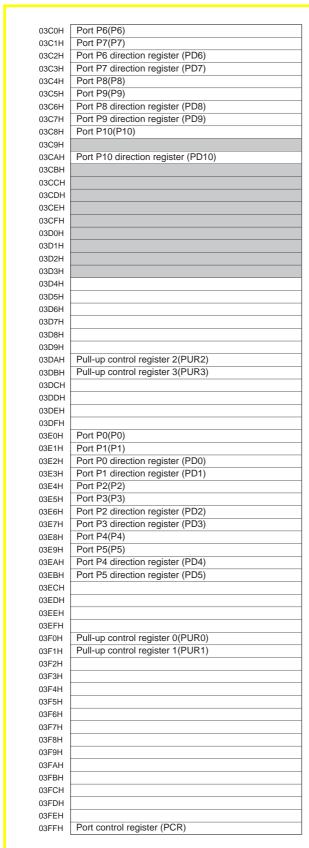

| Figure 2.1.3   | 3 Control register allocation 1                        | 10 |

| Figure 2.1.4   | 4 Control register allocation 2                        | 11 |

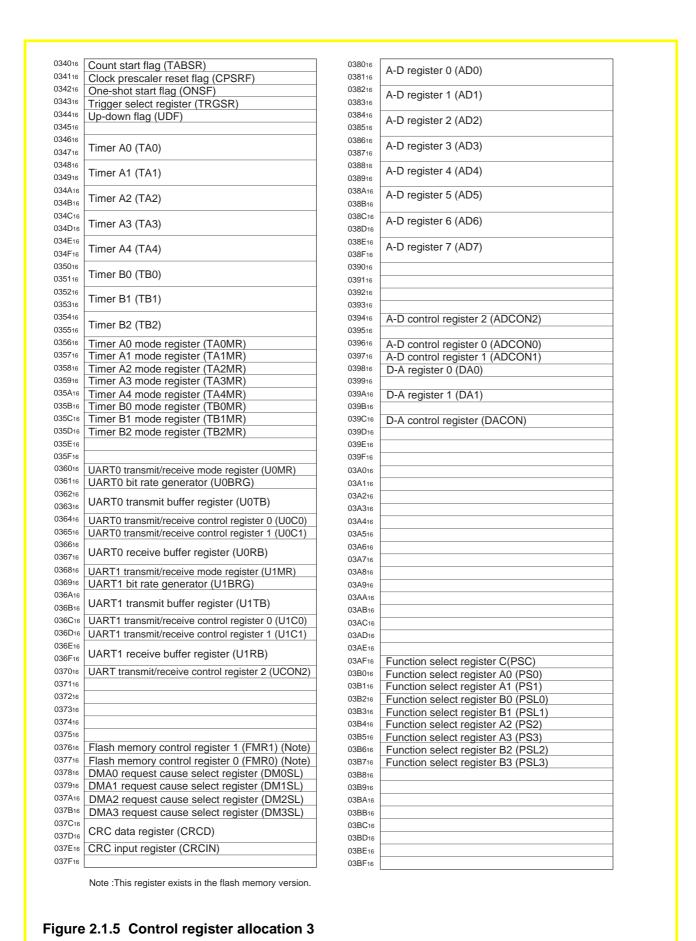

| Figure 2.1.5   | 5 Control register allocation 3                        | 12 |

| Figure 2.1.6   | 6 Control register allocation 4                        | 13 |

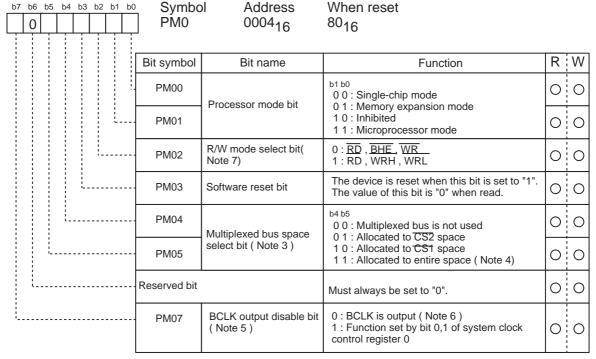

| Figure 2.1.7   | 7 Processor mode register 0                            | 14 |

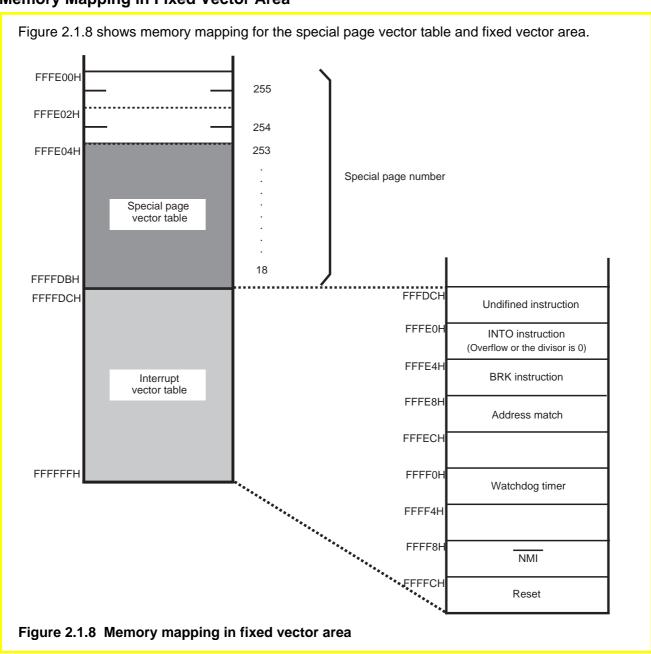

| Figure 2.1.8   | 8 Memory mapping in fixed vector area                  | 15 |

| 2.2 Register S | Set —                                                  |    |

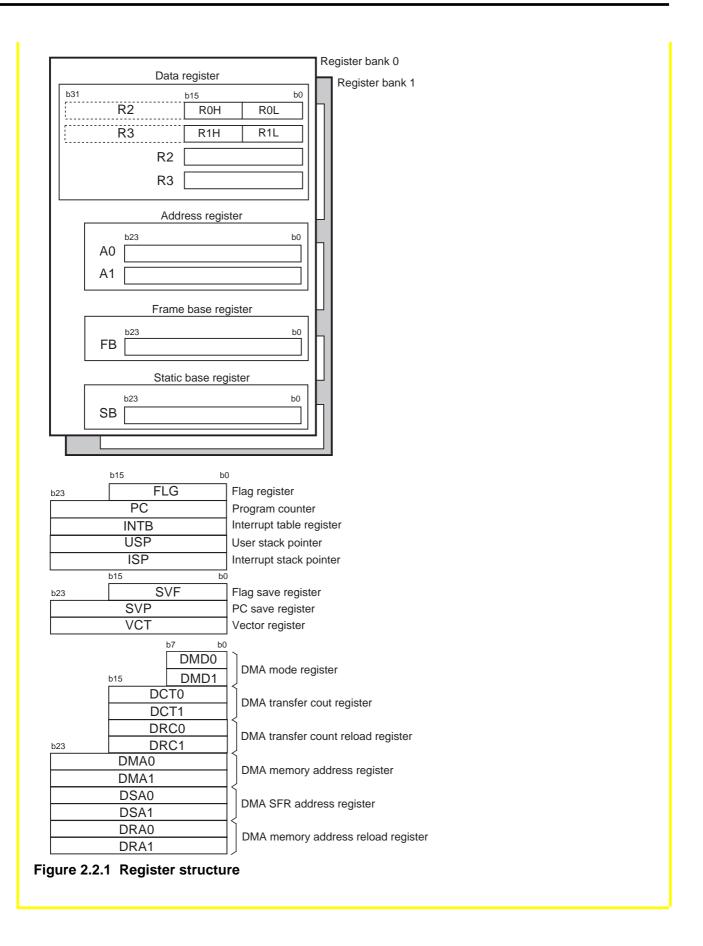

| Figure 2.2.    | 1 Register structure                                   | 18 |

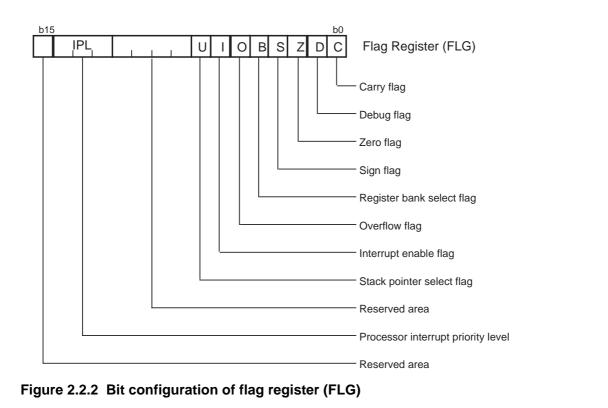

| Figure 2.2.2   | 2 Bit configuration of flag register (FLG)             | 20 |

| 2.3 Data Type  | es ————————————————————————————————————                |    |

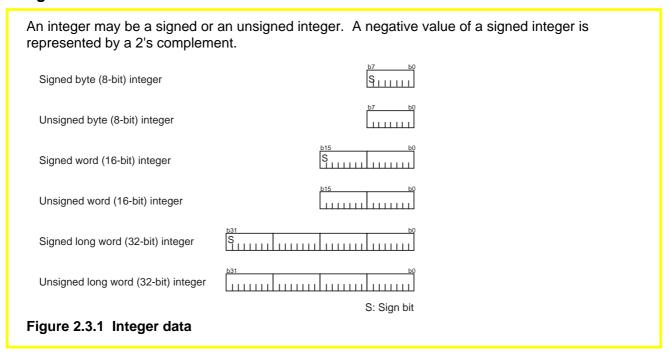

| Figure 2.3.    | 1 Integer data                                         | 22 |

| Figure 2.3.2   | 2 Decimal data                                         | 22 |

| Figure 2.3.3   | 3 String data                                          | 23 |

| Figure 2.3.4   | 4 Specification of register bits                       | 23 |

| Figure 2.3.5   | 5 Specification of memory bits                         | 23 |

| 2.4 Data Arra  | ingement ————————————————————————————————————          |    |

| Figure 2.4.    | 1 Data arrangement in register                         | 24 |

| Figure 2.4.2   | 2 Data arrangement in memory                           | 24 |

| 2.5 Addressir  | ng Modes ————————————————————————————————————          |    |

| Figure 2.5.    | 1 Absolute addressing                                  | 27 |

| Figure 2.5.2   | 2 Address register indirect addressing                 | 28 |

| Figure 2.5.3   | 3 Address register relative addressing 1               | 29 |

| Figure 2.5.4   | 4 Address register relative addressing 2               | 29 |

| Figure 2.5.5   | 5 Address register relative addressing 3               | 29 |

| Figure 2.5.6   | 6 SB relative addressing                               | 30 |

| Figure 2.5.7   | 7 FB relative addressing 1                             | 30 |

| Figure 2.5.8   | 8 FB relative addressing 2                             | 30 |

| Figure 2.5.9 SB relative and FB relative addressing                | 31  |

|--------------------------------------------------------------------|-----|

| Figure 2.5.10 Application example of SB relative addressing        | 32  |

| Figure 2.5.11 Application example of FB relative addressing        | 32  |

| Figure 2.5.12 SP relative addressing 1                             | 33  |

| Figure 2.5.13 SP relative addressing 2                             | 33  |

| Figure 2.5.14 Absolute indirect addressing                         | 35  |

| Figure 2.5.15 Two-stage address register indirect addressing       | 35  |

| Figure 2.5.16 Address register relative indirect addressing        | 36  |

| Figure 2.5.17 SB relative indirect addressing                      | 36  |

| Figure 2.5.18 FB relative indirect addressing 1                    | 37  |

| Figure 2.5.19 FB relative indirect addressing 2                    | 37  |

| Figure 2.5.20 Control register direct addressing                   | 38  |

| Figure 2.5.21 Program counter relative addressing 1                | 38  |

| Figure 2.5.22 Program counter relative addressing 2                | 38  |

| Figure 2.5.23 Program counter relative addressing 3                | 39  |

| Figure 2.5.24 Bit instruction absolute addressing 1                | 40  |

| Figure 2.5.25 Bit instruction absolute addressing 2                | 40  |

| Figure 2.5.26 Bit instruction register direct addressing           | 41  |

| Figure 2.5.27 Bit instruction FLG direct addressing                | 41  |

| Figure 2.5.28 Bit instruction address register indirect addressing | 42  |

| Figure 2.5.29 Bit instruction address register relative addressing | 42  |

| Figure 2.5.30 Bit instruction SB relative addressing               | 43  |

| Figure 2.5.31 Bit instruction FB relative addressing               | 44  |

| 2.6 Instruction Set                                                |     |

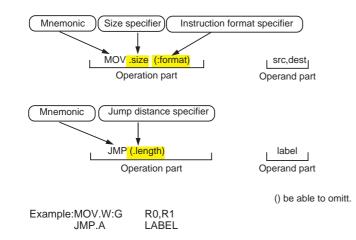

| Figure 2.6.1 Format of instruction description                     | 46  |

| Figure 2.6.2 Specifiers                                            | 46  |

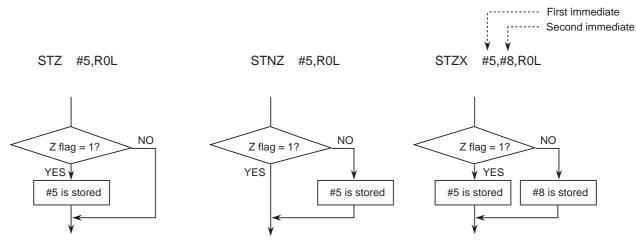

| Figure 2.6.3 Typical operations of conditional store instructions  | 69  |

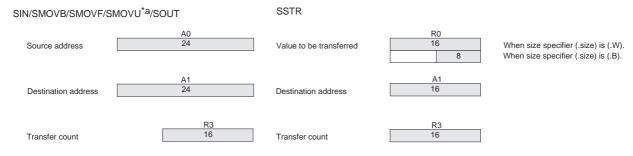

| Figure 2.6.4 Setting registers for string instructions             | 70  |

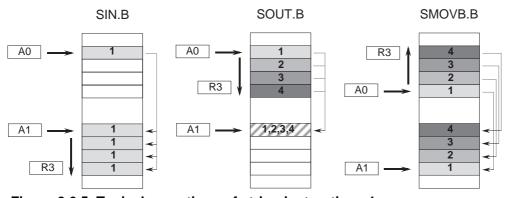

| Figure 2.6.5 Typical operations of string instructions 1           | 70  |

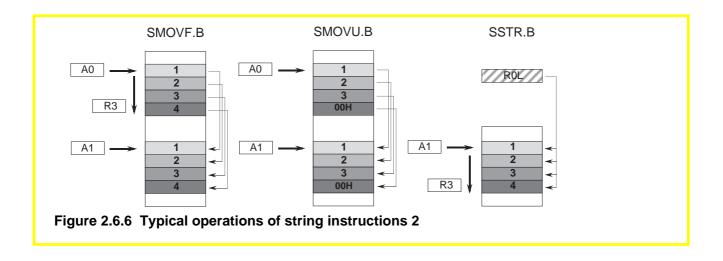

| Figure 2.6.6 Typical operations of string instructions 2           | 71  |

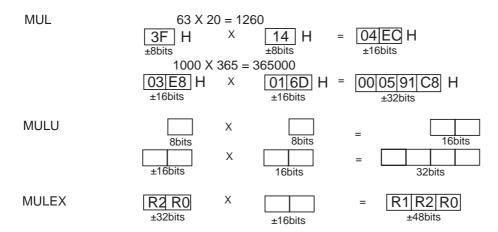

| Figure 2.6.7 Typical operations of multiply instructions           | 72  |

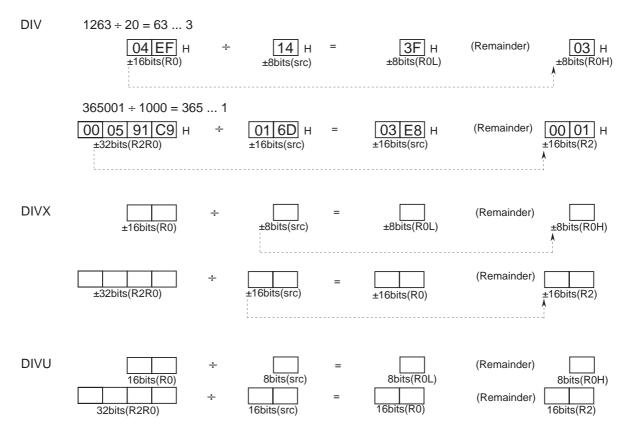

| Figure 2.6.8 Typical operations of divide instructions             | 73  |

|                                                                    |     |

| Chapter 3 Functions of Assembler                                   |     |

| •                                                                  |     |

| 3.1 Outline of AS308 System                                        |     |

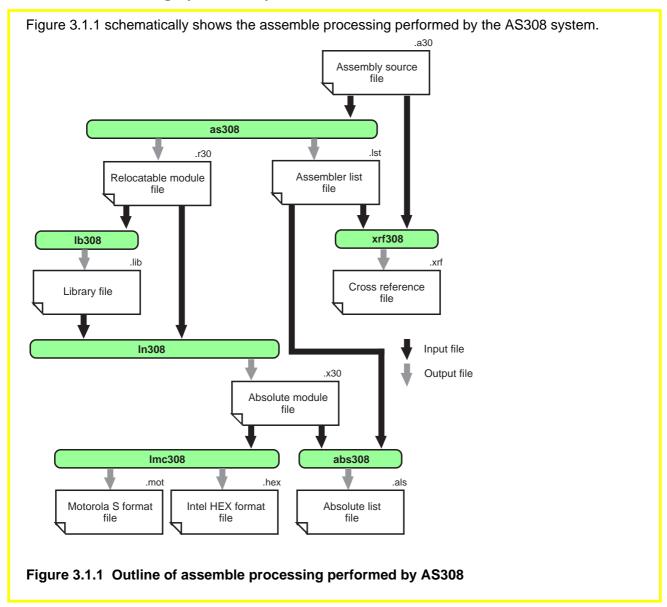

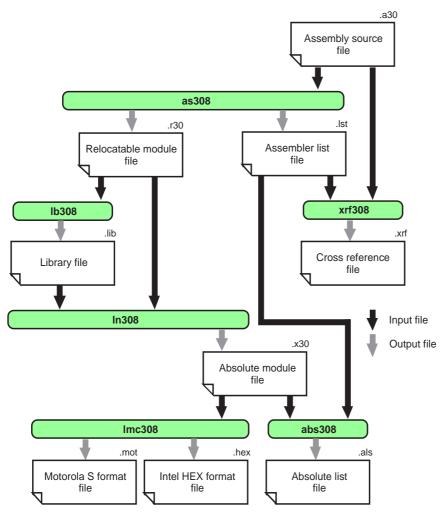

| Figure 3.1.1 Outline of assemble processing performed by AS308     |     |

| 3.2 Method for Writing Source Program                              |     |

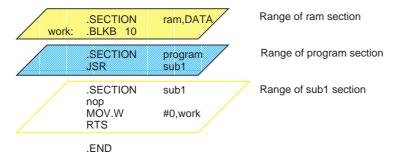

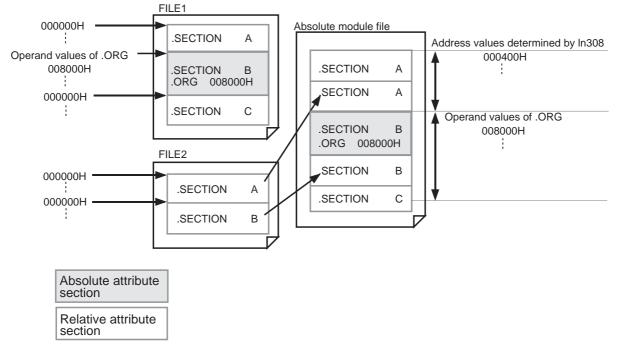

| Figure 3.2.1 Range of sections in AS308 system                     |     |

| Figure 3.2.2 Example of address control                            |     |

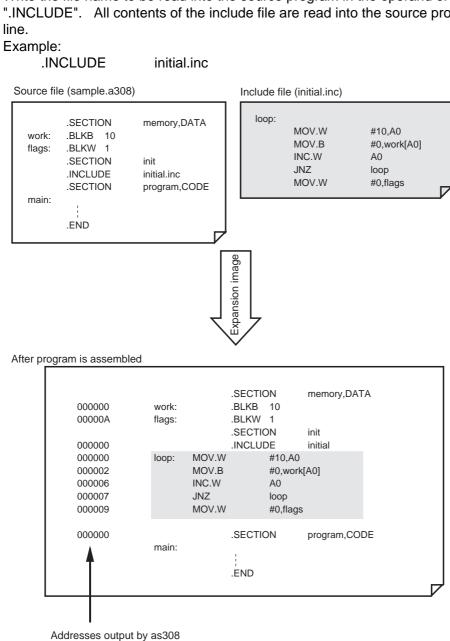

| Figure 3.2.3 Reading include file into source program              | 121 |

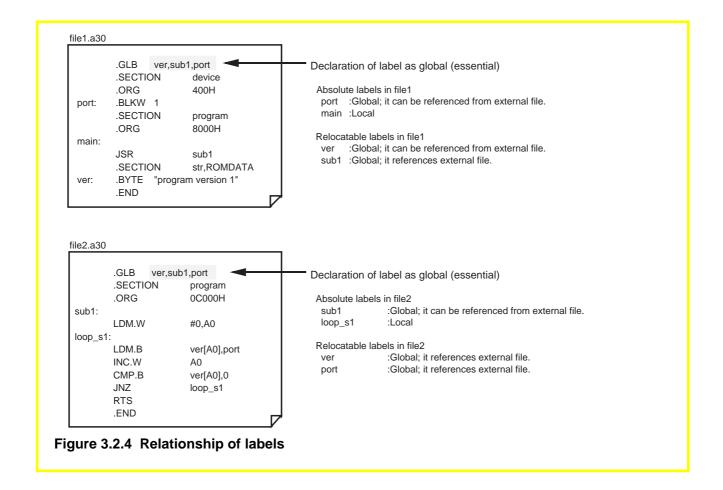

| Figure 3.2.4     | Relationship of labels                                                         | 123 |

|------------------|--------------------------------------------------------------------------------|-----|

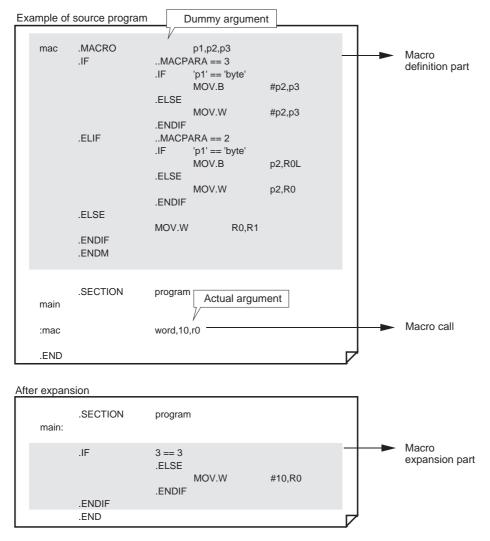

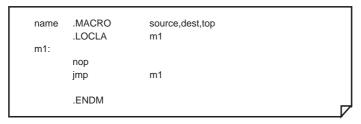

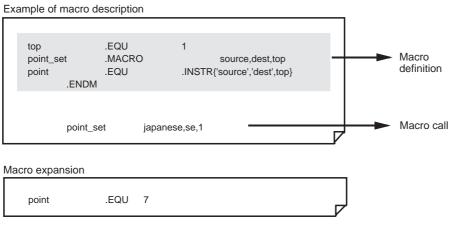

| Figure 3.2.5     | Example 1 of macro definition and macro call                                   | 132 |

| Figure 3.2.6     | Example 2 of macro definition and macro call                                   | 132 |

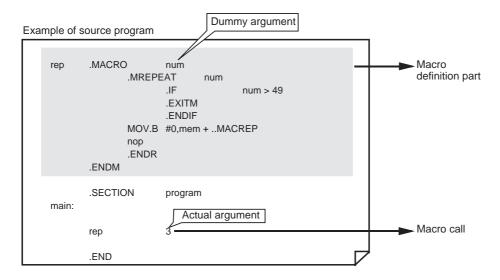

| Figure 3.2.7     | Example 3 of macro definition and macro call                                   | 133 |

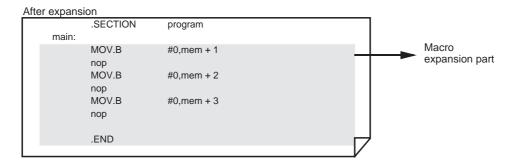

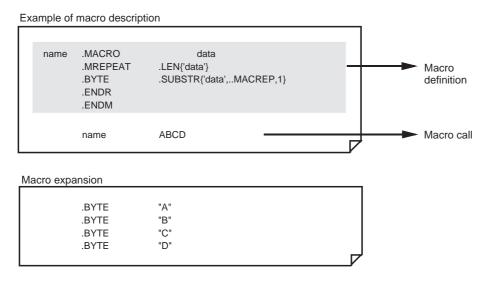

| Figure 3.2.8     | Example of .LEN statement                                                      | 136 |

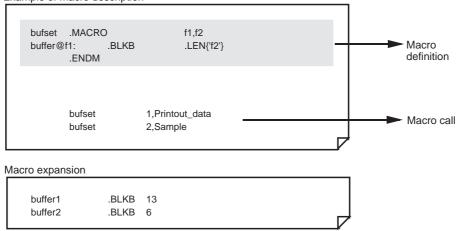

| Figure 3.2.9     | Example of .INSTR statement                                                    | 136 |

| Figure 3.2.1     | 0 Example of .SUBSTR statement                                                 | 137 |

| Chapter 4        | Programming Style                                                              |     |

| 4.1 Hardware     | Definition                                                                     |     |

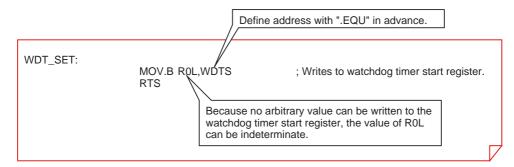

| Figure 4.1.1     | Example of SFR area definition by ".EQU"                                       | 144 |

| Figure 4.1.2     | Example of SFR area definition by ".BLKB"                                      | 145 |

| Figure 4.1.3     | Example for setting up a work area                                             | 147 |

| Figure 4.1.4     | Example for setting a data table                                               | 148 |

| Figure 4.1.5     | Example for retrieving data table                                              | 148 |

| Figure 4.1.6     | Example for setting up sections                                                | 149 |

| Figure 4.1.7     | Description example 1 for initial setting                                      | 153 |

| 4.2 Initial Sett | ing the CPU                                                                    |     |

| Figure 4.2.1     | Example for setting the processor mode and system clock                        | 154 |

| Figure 4.2.2     | Example for setting function select registers                                  | 155 |

| Figure 4.2.3     | Example for initial setting a work area                                        | 156 |

| Figure 4.2.4     | Example for initial setting ports                                              | 157 |

| Figure 4.2.5     | Example for setting timer                                                      | 157 |

| -                | DMAC-related registers                                                         |     |

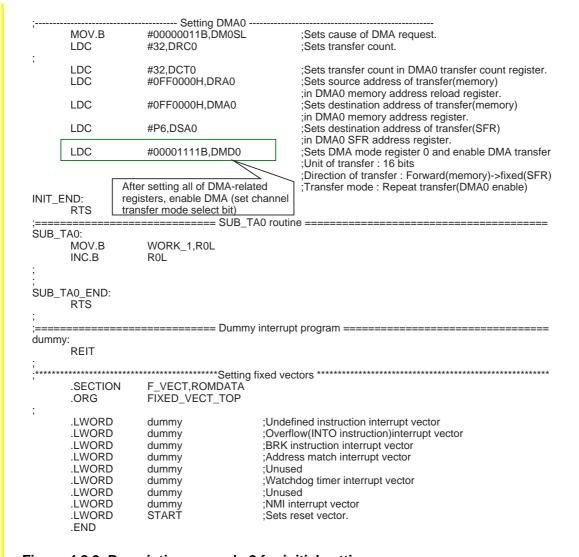

| Figure 4.2.7     | Example 1 for setting the DMA controller                                       | 159 |

| •                | Example 1 for setting the DMA controller                                       |     |

| Figure 4.2.9     | Description example 2 for initial setting                                      | 163 |

| 4.3 Setting wh   | en using Interrupts —                                                          |     |

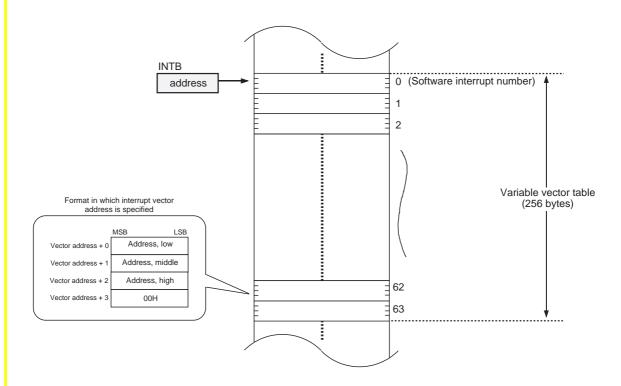

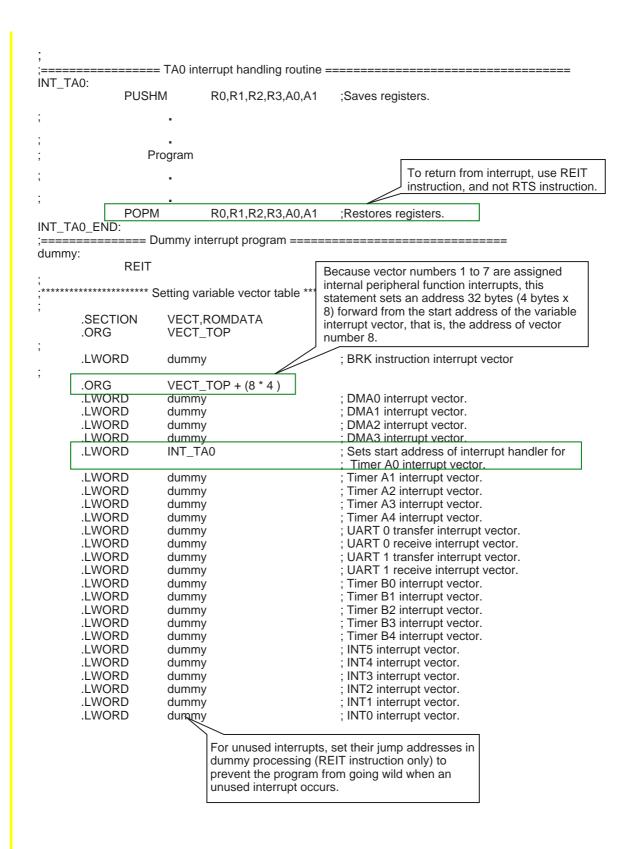

| Figure 4.3.1     | Variable vector table                                                          | 165 |

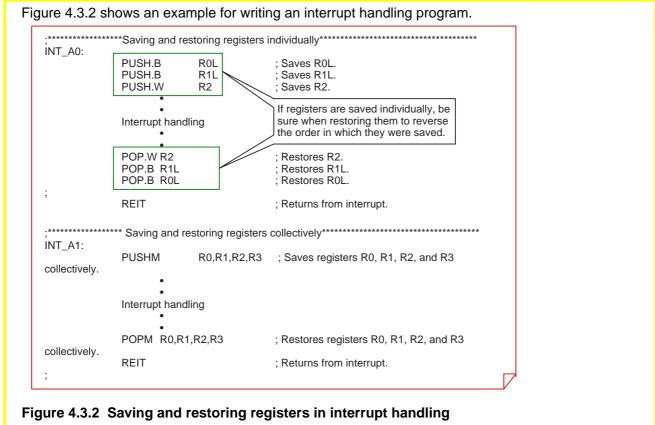

| Figure 4.3.2     | Saving and restoring registers in interrupt handling                           | 168 |

| Figure 4.3.3     | Saving and restoring registers by register bank switchover                     | 169 |

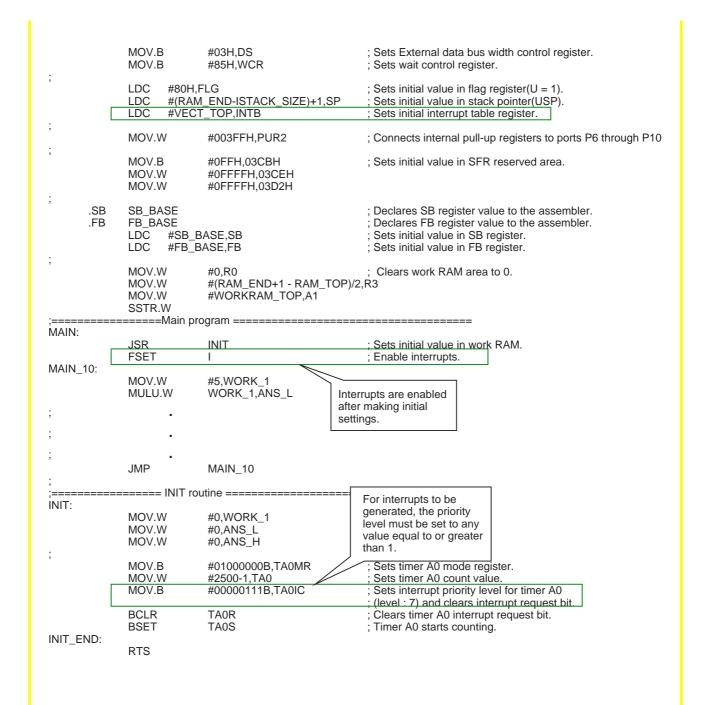

| Figure 4.3.4     | Sample program 3(Using interrupt)                                              | 173 |

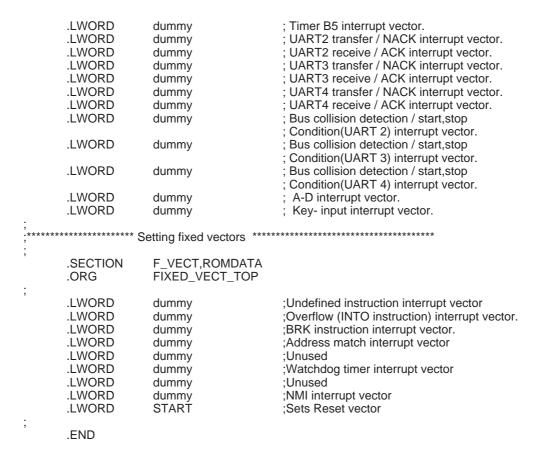

| Figure 4.3.5     | Interrupt number assignments                                                   | 174 |

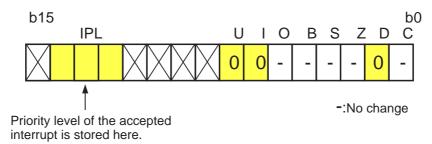

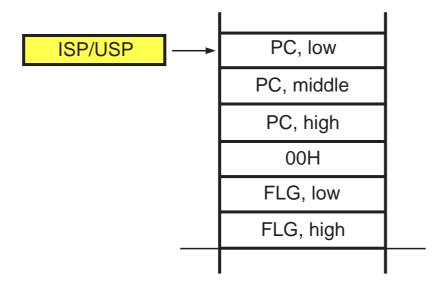

| Figure 4.3.6     | When a peripheral I/O interrupt or an INT instruction interrupt using software |     |

|                  | interrupt numbers 0 through 31                                                 |     |

|                  |                                                                                | 175 |

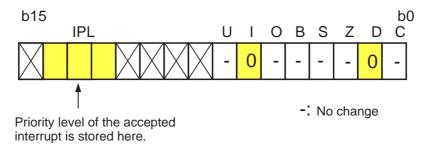

| Figure 4.3.7     | When an INT instruction interrupt using software interrupt numbers 32          |     |

|                  | through 63                                                                     |     |

|                  | English and the Balance of                                                     |     |

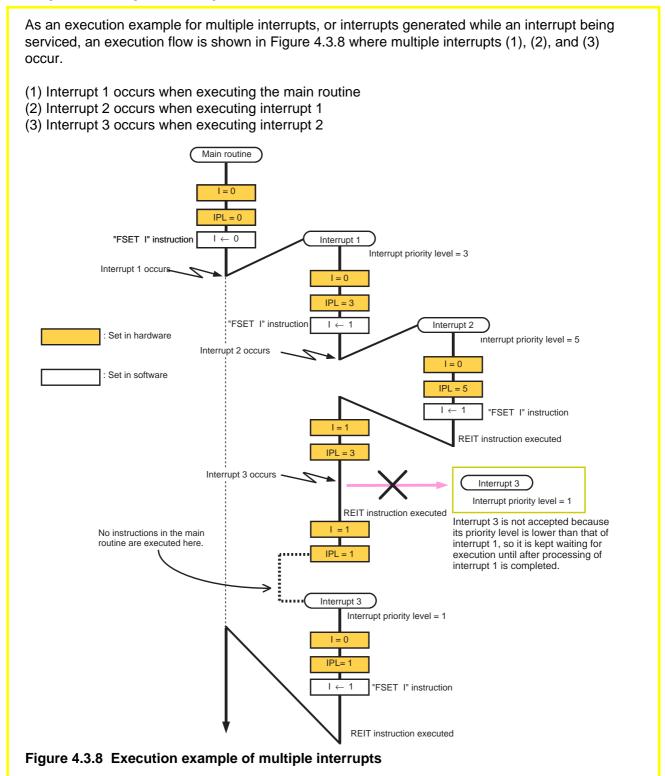

| FIGURE 4 3 8     | Execution example of multiple interrupts                                       | 1/7 |

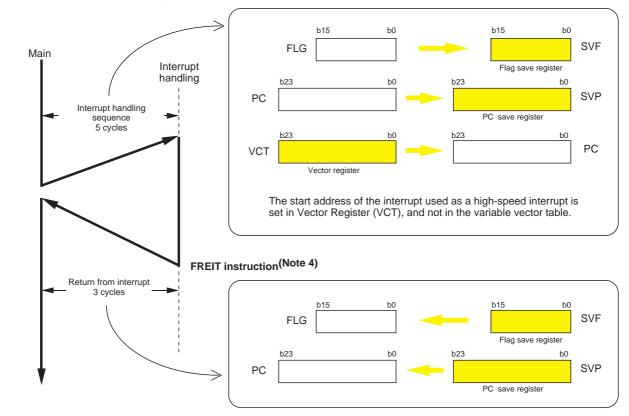

| Figure 4.3.9 Operation of a high-speed interrupt                                | 178         |

|---------------------------------------------------------------------------------|-------------|

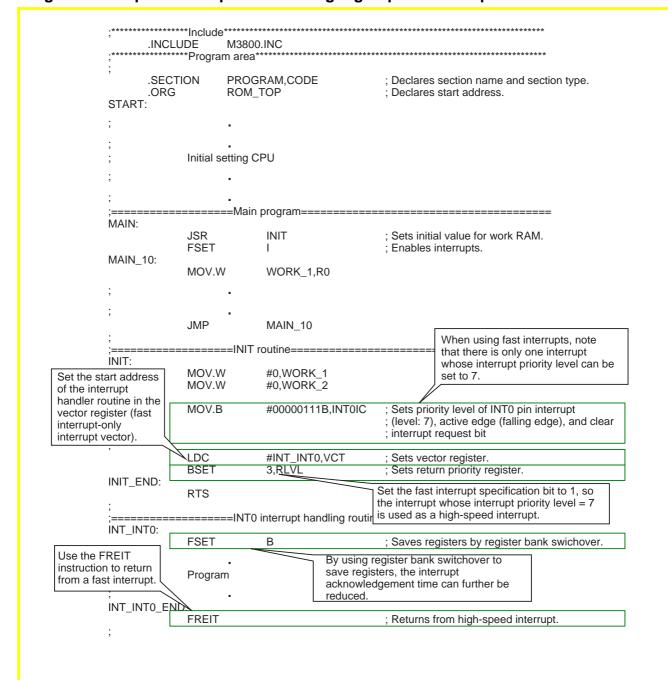

| Figure 4.3.10 Program example when using a high-speed interrupt                 | 181         |

| 4.4 Dividing Source File                                                        |             |

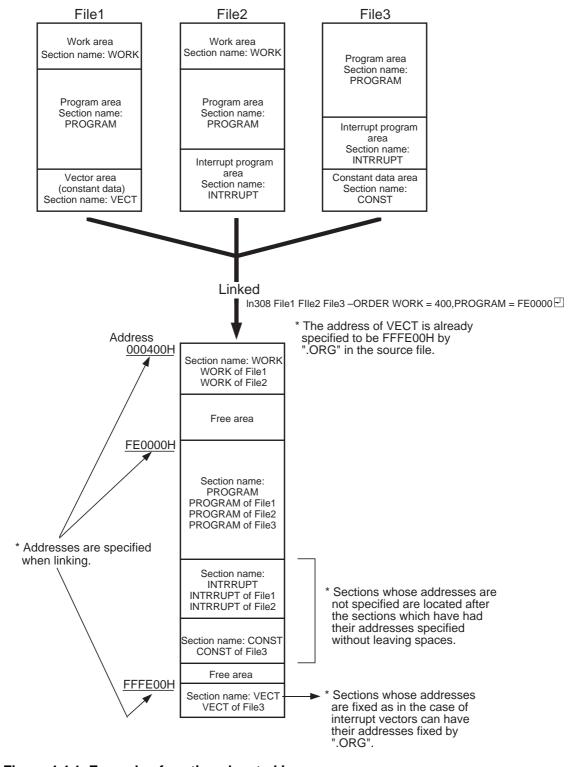

| Figure 4.4.1 Example of sections located in memory                              | 183         |

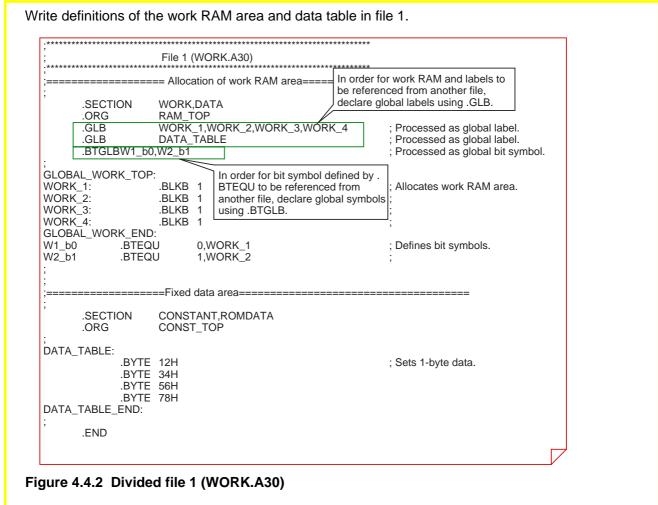

| Figure 4.4.2 Divided file 1 (WORK.A30)                                          |             |

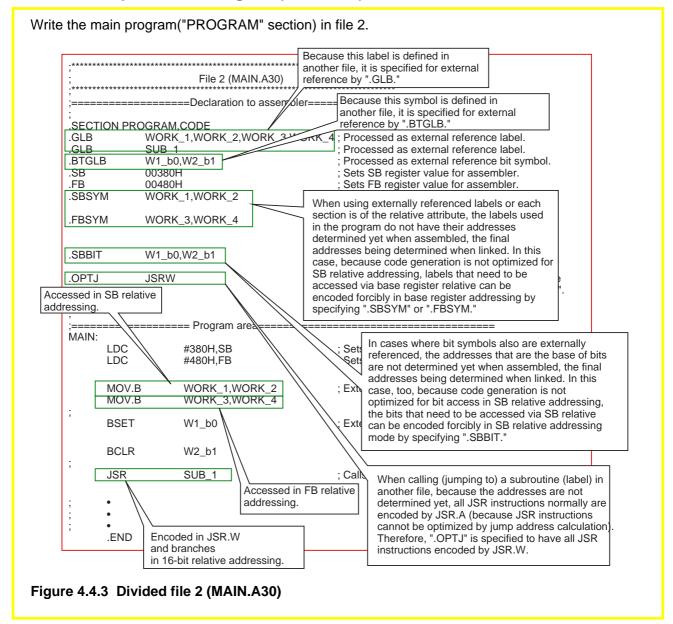

| Figure 4.4.3 Divided file 2 (MAIN.A30)                                          |             |

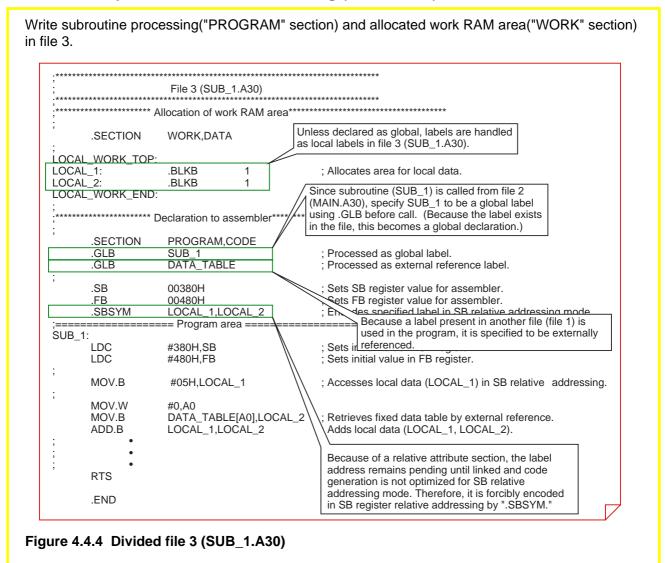

| Figure 4.4.4 Divided file 3 (SUB_1.A30)                                         |             |

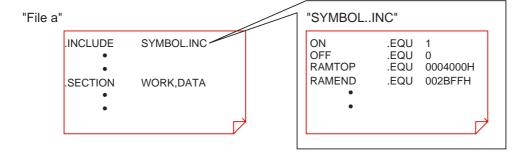

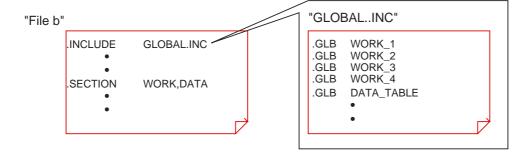

| Figure 4.4.5 Example of include file                                            | 188         |

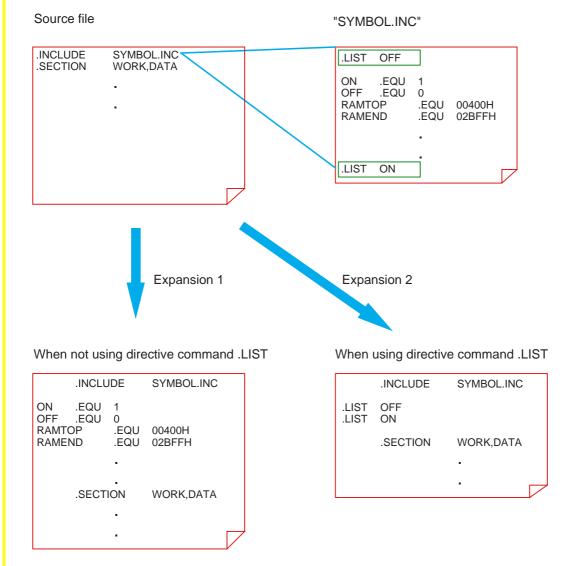

| Figure 4.4.6 Utilization of directive command .LIST                             | 189         |

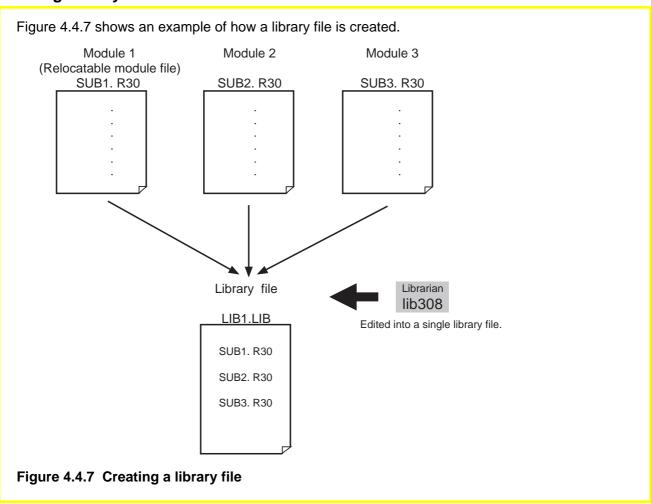

| Figure 4.4.7 Creating a library file                                            | 190         |

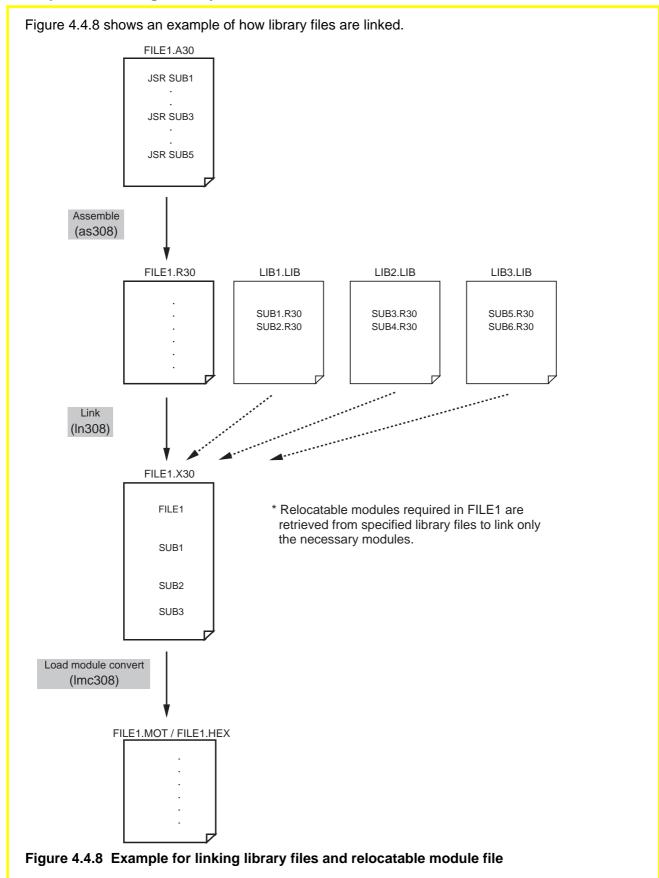

| Figure 4.4.8 Example for linking library files and relocatable module file      | 191         |

| 4.5 A Little Tips(Programing technique)                                         |             |

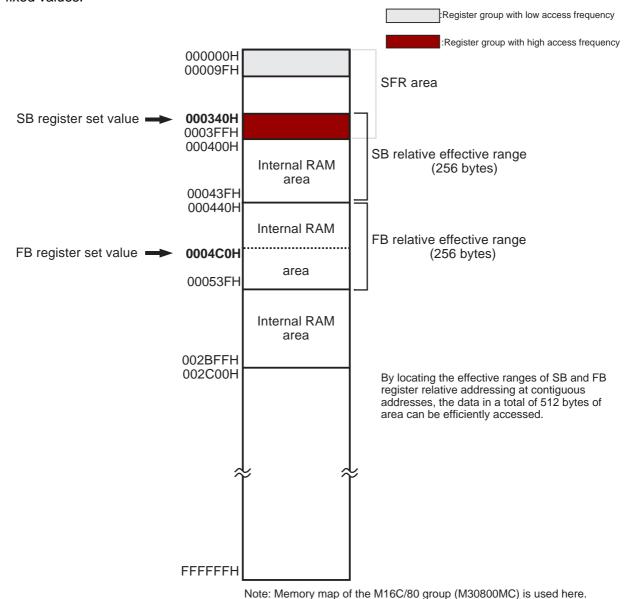

| Figure 4.5.1 Example for setting SB and FB registers as having fixed values     | 192         |

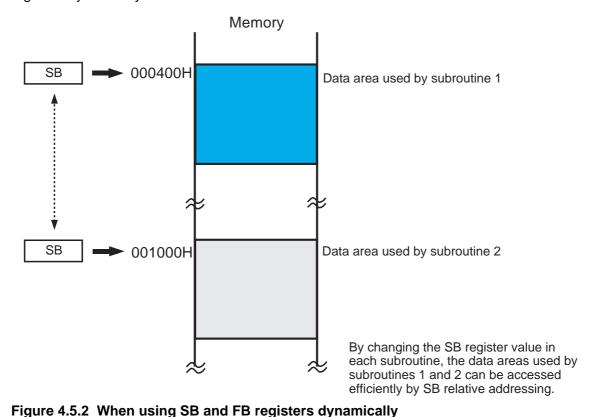

| Figure 4.5.2 When using SB and FB registers dynamically                         | 193         |

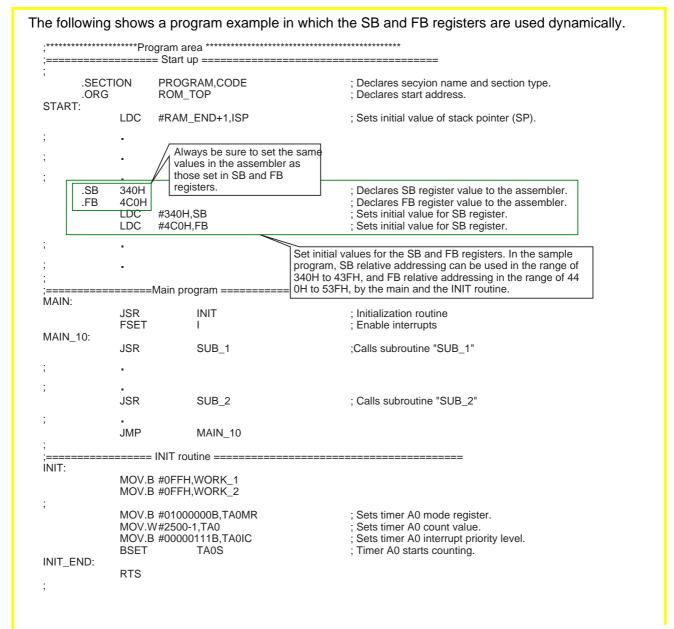

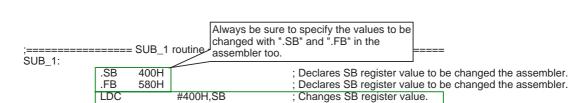

| Figure 4.5.3 Program example for using SB and FB registers dynamically          | 195         |

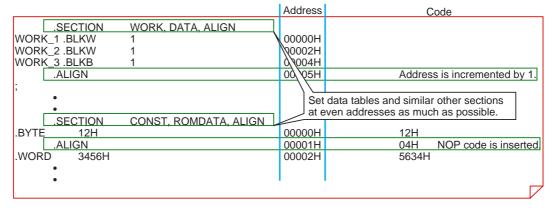

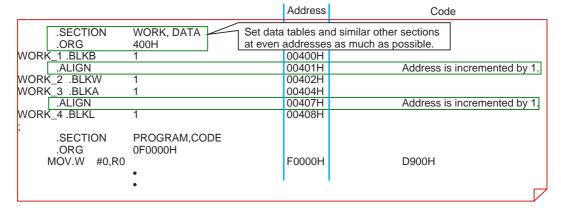

| Figure 4.5.4 Example of alignment specification                                 | 197         |

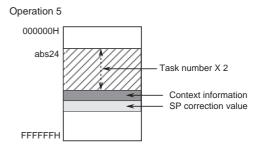

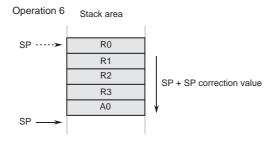

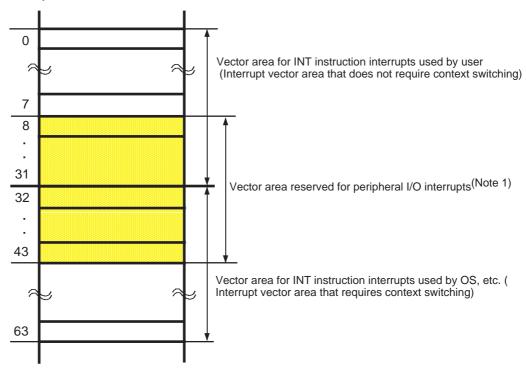

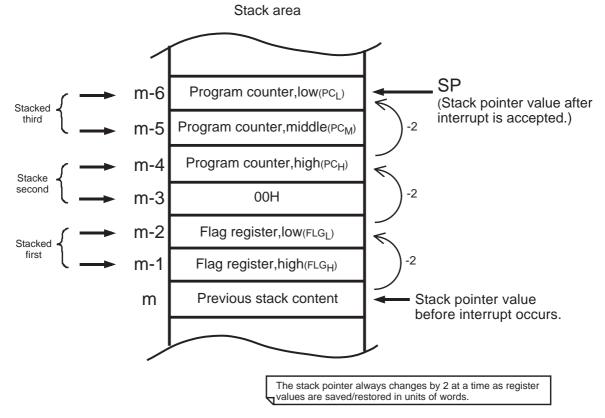

| Figure 4.5.5 Stack operation and status when an interrupt is accepted           | 199         |

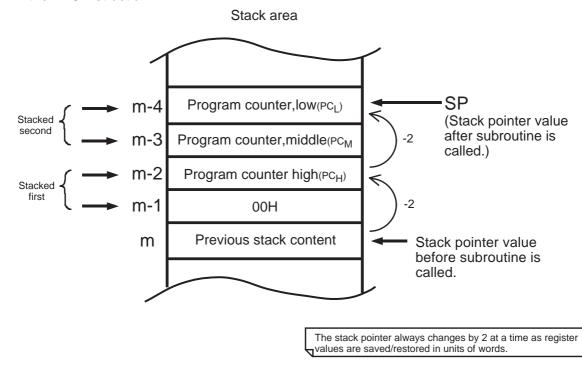

| Figure 4.5.6 Stack operation and status when a subroutine is called             |             |

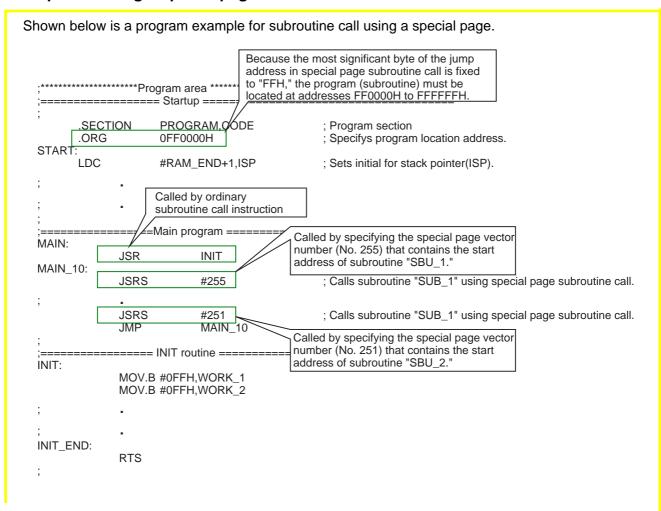

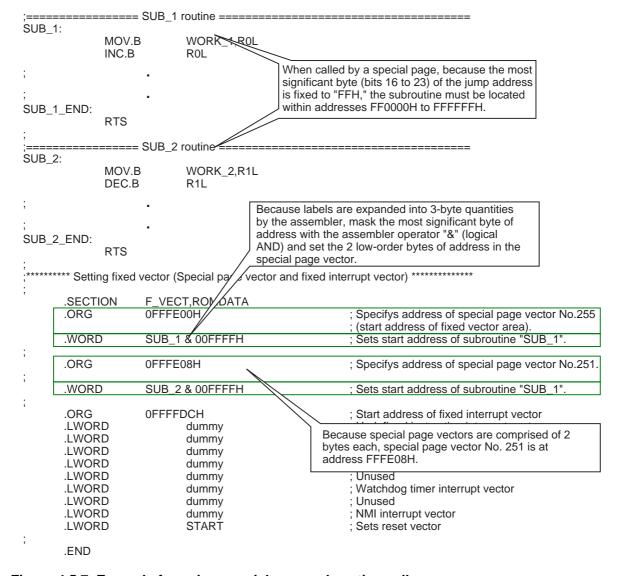

| Figure 4.5.7 Example for using special page subroutine call                     |             |

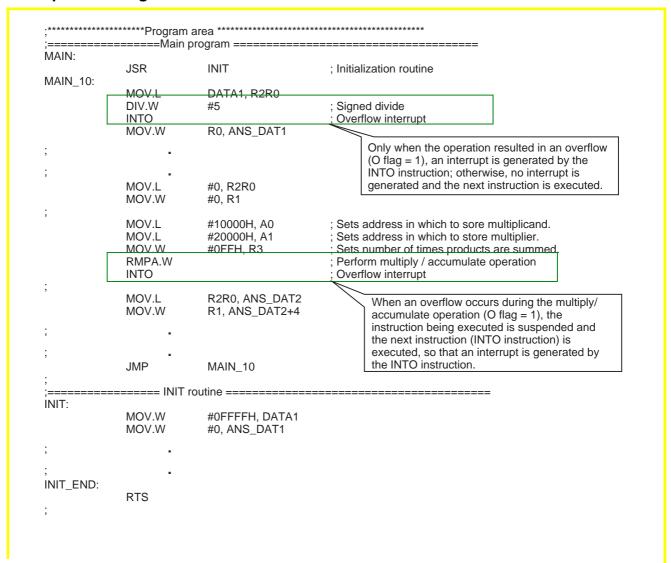

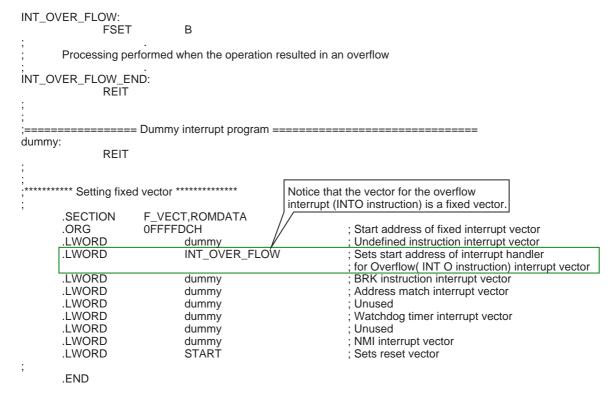

| Figure 4.5.8 Example for using INTO (software interrupt) instruction            |             |

| Figure 4.5.9 Operation flow when program runaway is detected                    |             |

| Figure 4.5.10 Example of runaway detection program 1                            |             |

| Figure 4.5.11 Example of runaway detection program 2                            |             |

| Figure 4.5.12 Runaway detection using software interrupt instructions           |             |

| Figure 4.5.13 Example for specifying section data location with -LOC option     | 209         |

| 4.6 Standard processing program ————————————————————————————————————            |             |

| Figure 4.6.1 Sample program for conditional branching based on specified bit st |             |

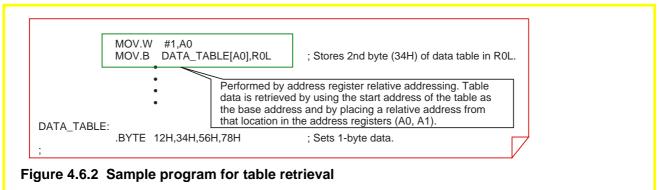

| Figure 4.6.2 Sample program for table retrieval                                 |             |

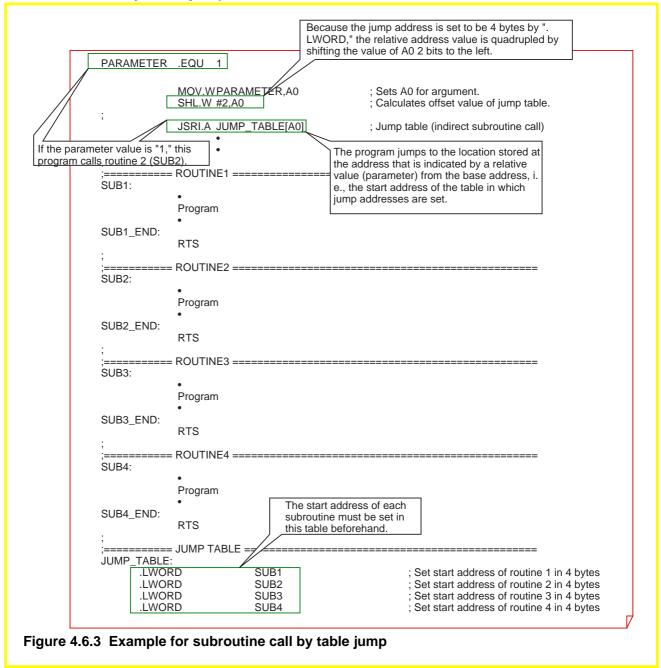

| Figure 4.6.3 Example for subroutine call by table jump                          | 211         |

| Appendix Command input form and                                                 |             |

| command parameters in AS308                                                     | system      |

| Annual din A. Composition Object Files                                          |             |

| Appendix A Generating Object Files                                              |             |

| Figure A.O. Francels of good with the                                           | • •         |

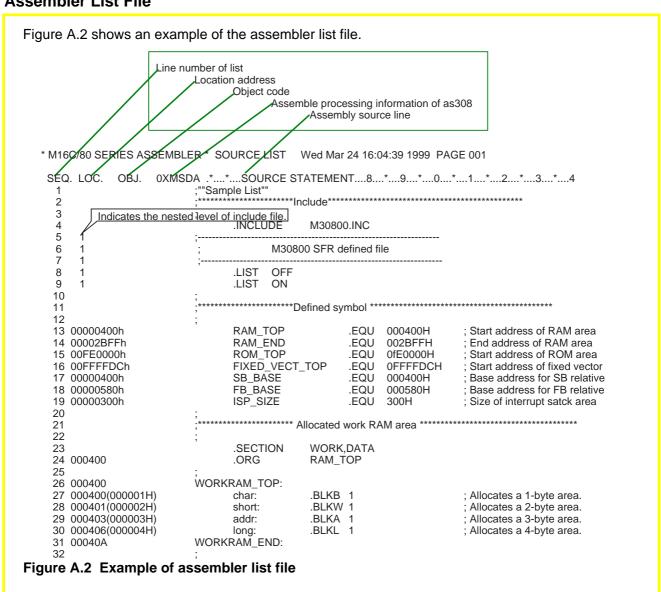

| Figure A.2. Example of assembler list file                                      | • •         |

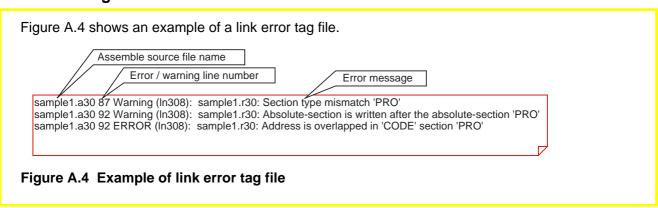

| Figure A.4. Example of link error tog file                                      | • •         |

| Figure A.F. Example of link error tag file                                      |             |

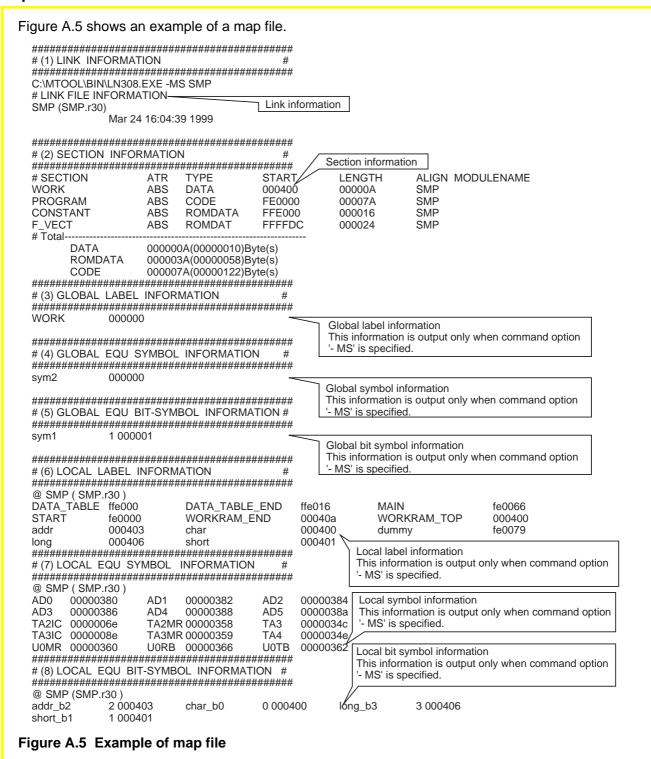

| Figure A.5 Example of map file                                                  | Appenaix-11 |

# **Table of contents for table**

## **Chapter 1 Overview of M16C/80 Series**

| 1.1 Features of M16C/80 Series                             |    |

|------------------------------------------------------------|----|

| 1.2 Outline of M16C/80 Group                               |    |

| Table 1.2.1 Outline Specifications of M16C/80 Group        | 4  |

| Table 1.2.2 Register Structure of M16C/80 Series           | 5  |

|                                                            |    |

| Chapter 2 CPU Programming Model                            |    |

| 2.1 Address Space                                          |    |

| 2.2 Register Set                                           |    |

| Table 2.2.1 Register Status after Reset Cleared            | 21 |

| 2.3 Data Types                                             |    |

| 2.4 Data Arrangement                                       |    |

| 2.5 Addressing Modes                                       | _  |

| Table 2.5.1 Addressing Modes of M16C/80 Series 1           | 25 |

| Table 2.5.2 Addressing Modes of M16C/80 Series 2           |    |

| Table 2.5.3 Relative Address Ranges of Relative Addressing | 34 |

| 2.6 Instruction Set                                        |    |

| Table 2.6.1 Generic format                                 | 47 |

| Table 2.6.2 Quick format                                   | 47 |

| Table 2.6.3 Short format                                   | 47 |

| Table 2.6.4 Zero format                                    | 47 |

| Table 2.6.5 4 Bit Transfer Instruction                     | 68 |

| Table 2.6.6 Conditional Store Instruction                  | 69 |

| Table 2.6.7 String Instruction                             | 70 |

| Table 2.6.8 Multiply Instruction                           | 72 |

| Table 2.6.9 Divide Instruction                             | 73 |

| Table 2.6.10 Difference between DIV and DIVX Instructions  | 74 |

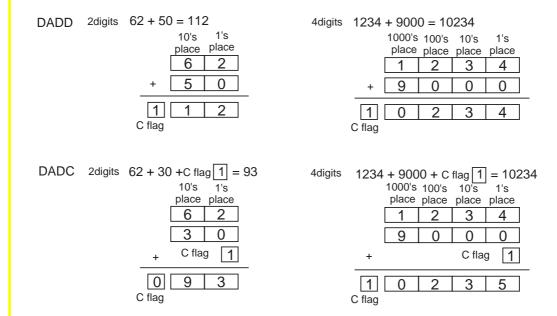

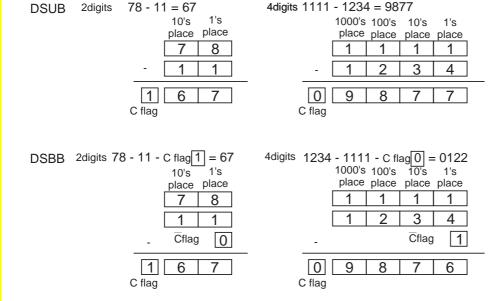

| Table 2.6.11 Decimal Add Instruction                       | 75 |

| Table 2.6.12 Decimal Subtract Instruction                  | 76 |

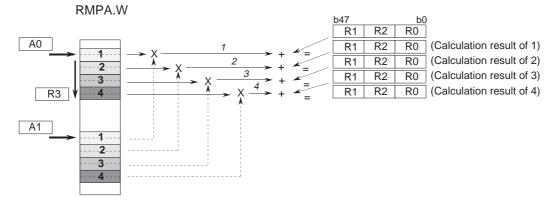

| Table 2.6.13 Sum of Products Calculate Instruction         |    |

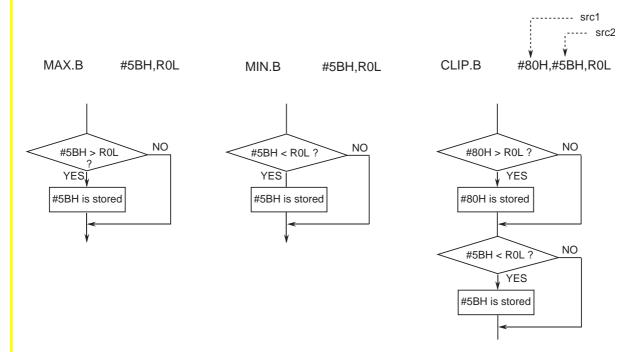

| Table 2.6.14 MAX, MIX, and CLIP instructions               | 78 |

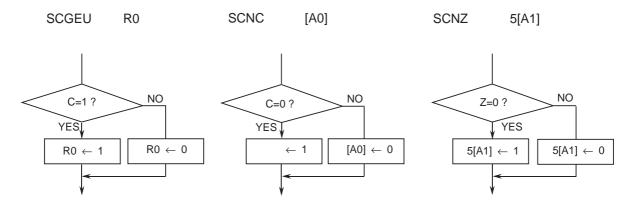

| Table 2.6.15 SCcnd instruction                             |    |

| Table 2.6.16 Unconditional Branch Instruction              |    |

| Table 2.6.17 Indirect Branch Instruction                   | 81 |

| Table 2.6.18 Special Page Branch Instruction               | 82 |

| Table 2.6.19 Conditional Branch Instruction                                | 83  |

|----------------------------------------------------------------------------|-----|

| Table 2.6.20 Add (Subtract) & Conditional Branch Instruction               | 84  |

| Table 2.6.21 Logical Bit Manipulating Instruction                          | 85  |

| Table 2.6.22 Conditional Bit Transfer Instruction                          | 86  |

| Table 2.6.23 Sign-extension instruction                                    | 87  |

| Table 2.6.24 Index instruction                                             | 88  |

| Table 2.6.25 Stack Frame Build Instruction                                 | 90  |

| Table 2.6.26 Deallocate Stack Frame Instruction                            | 91  |

| Table 2.6.27 OS Support Instructions                                       | 92  |

| 2.7 Outline of Interrupt                                                   |     |

| Chapter 3 Functions of Assembler                                           |     |

| 3.1 Outline of AS308 System —                                              |     |

| Table 3.1.1 List of Input/output Files                                     | 108 |

| 3.2 Method for Writing Source Program ———————————————————————————————————— |     |

| Table 3.2.1 Types of Names Defined by User                                 | 112 |

| Table 3.2.2 Description of Operands                                        | 113 |

| Table 3.2.3 Description Range of Floating-point Numbers                    |     |

| Table 3.2.4 List of Operators                                              | 115 |

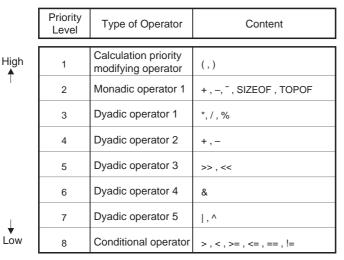

| Table 3.2.5 Calculation Priority                                           |     |

| Table 3.2.6 Types of Lines                                                 |     |

| Table 3.2.7 Types of Sections                                              |     |

| Table 3.2.8 Section Attributes                                             |     |

| Table 3.2.9 Replacement Instruction List                                   | 140 |

| Chapter 4 Programming Style                                                |     |

| 4.1 Hardware Definition —                                                  |     |

| 4.2 Initial Setting the CPU                                                |     |

| 4.3 Setting when using Interrupts —                                        |     |

| 4.4 Dividing Source File                                                   |     |

| 4.5 A Little Tips(Programing technique)                                    |     |

| 4.6 Standard processing program —                                          |     |

# Appendix Command input form and command parameters in AS308 system

### **Appendix A Generating Object Files**

| Table A.1 | Command Options of as308  | . Appendix-4 |

|-----------|---------------------------|--------------|

| Table A.2 | Command Options of In308  | . Appendix-9 |

| Table A.3 | Command Options of Imc308 | Appendix-12  |

# **Chapter 1**

### Overview of M16C/80 Series

- 1.1 Features of M16C/80 Series

- 1.2 Outline of M16C/80 Group

#### 1.1 Features of M16C/80 Series

The M16C/80 series is a line of single-chip microcomputers that have been developed for use in built-in equipment. This section describes the features of the M16C/80 series.

#### Features of the M16C/80 series

The M16C/80 series has its frequently used instructions placed in a 1-byte op-code. For this reason, it allows you to write a highly memory efficient program.

Furthermore, although the M16C/80 series is a 16-bit microcomputer, it can perform 1, 4, and 8-bit processing efficiently. Especially, 32-bit processing is handled more efficiently than in the M16C/60 series. The M16C/80 series has many instructions that can be executed in one clock period. For this reason, it is possible to write a high-speed processing program.

The M16C/80 series provides 1 M bytes of linear addressing space. Therefore, the M16C/80 series is also suitable for applications that require a large program size.

The features of the M16C/80 series can be summarized as follows:

- (1) The M16C/80 series allows you to create a memory-efficient program without requiring a large memory capacity.

- (2) The M16C/80 series allows you to create a high-speed processing program.

- (3) The M16C/80 series provides 1 M bytes of addressing space, making it suitable for even large-capacity applications.

### 1.2 Outline of M16C/80 Group

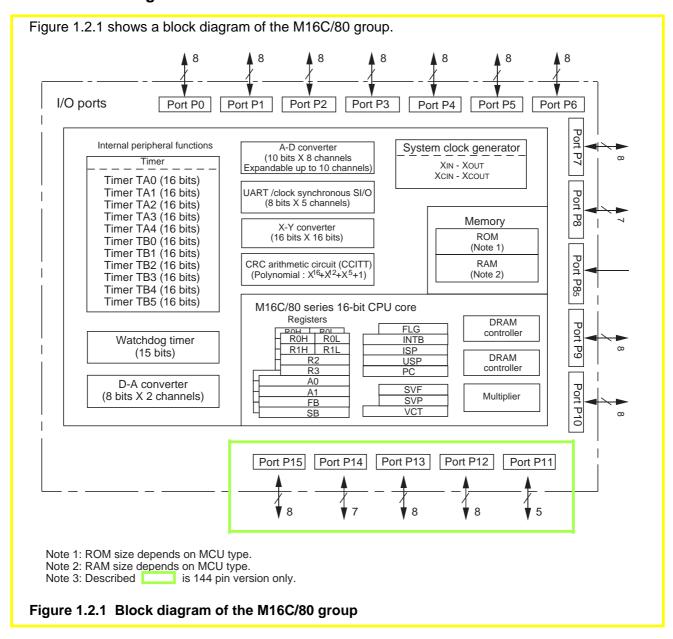

This section introduces the M16C/80 group by way of explaining the internal configuration of the M16C/80 series. The M16C/80 group is a product that comprises the basis of the M16C/80 series. For details about this product, refer to the data sheets and user's manuals.

#### **Internal Block Diagram**

### **Outline Specifications of the M16C/80 Group**

Table 1.2.1 lists the outline specifications of the M16C/80 group.

Table 1.2.1 Outline Specifications of M16C/80 Group

| Item                                |                              | Performance                                           |

|-------------------------------------|------------------------------|-------------------------------------------------------|

| Number of basic instructions        |                              | 106 instructions                                      |

| Shortest instruction execution time |                              | 50ns(f(XIN)=20MHz)                                    |

| Memory                              | ROM                          | 128K bytes                                            |

| capacity                            | RAM                          | 10K bytes                                             |

| I/O port                            | P0 to P10 (except P85)       | 8 bits x 10, 7 bits x 1 (100-pin version)             |

|                                     | P0 to P15 (except P85)       | 8 bits x 10, 7 bits x 1, 5 bits x 1 (144-pin version) |

| Input port                          | P85                          | 1 bit x 1                                             |

| Multifunction                       | TA0, TA1, TA2, TA3,TA4       | 16 bits x 5                                           |

| timer                               | TB0, TB1, TB2, TB3, TB4, TB5 | 16 bits x 6                                           |

| Serial I/O                          | UART0, UART1, UART2,         | (UART or clock synchronous) x 5                       |

|                                     | UART3, UART4                 |                                                       |

| A-D converter                       |                              | 10 bits x (8 + 2) channels                            |

| D-A converter                       |                              | 8 bits x 2                                            |

| DMAC                                |                              | 4 channels                                            |

| DRAM controller                     |                              | CAS before RAS refresh, self-refresh, EDO, FP         |

| CRC calculation circuit             |                              | CRC-CCITT                                             |

| X-Y converter                       |                              | 16 bits X 16 bits                                     |

| Watchdog timer                      |                              | 15 bits x 1 (with prescaler)                          |

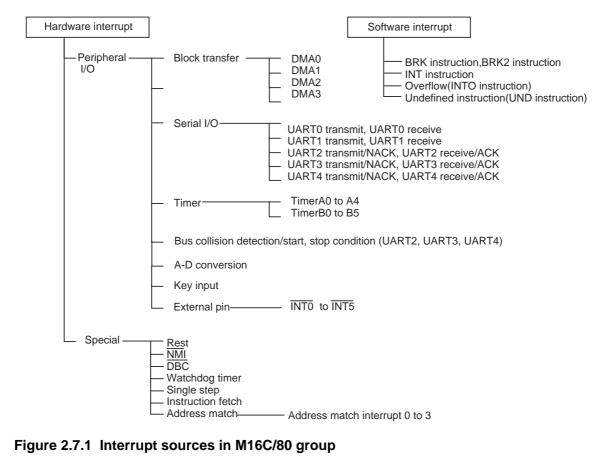

| Interrupt                           |                              | 29 internal and 8 external sources, 4 software        |

|                                     |                              | sources, 7 levels                                     |

| Clock generating circuit            |                              | 2 built-in clock generation circuits                  |

|                                     |                              | (built-in feedback resistor, and external ceramic or  |

|                                     |                              | quartz oscillator)                                    |

| Memory expansion                    |                              | Available (up to 16 Mbytes)                           |

Note: The above specifications are for the M30800MC. For details the memory size, refer to the data sheet and user's manual.

#### **Register Structure**

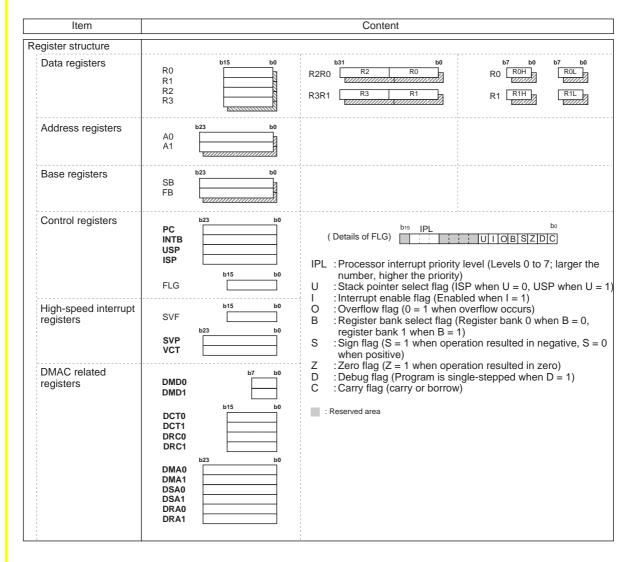

Table 1.2.2 shows the register structure of the M16C/80 series. Eight registers--R0, R1, R2, R3, A0, A1, SB, and FB--are available in two sets each. These sets are switched over by a register bank select flag.

Table 1.2.2 Register Structure of M16C/80 Series

**MEMO**

# **Chapter 2**

### **CPU Programming Model**

- 2.1 Address Space

- 2.2 Register Sets

- 2.3 Data Types

- 2.4 Data Arrangement

- 2.5 Addressing Modes

- 2.6 Instruction Set

- 2.7 Outline of Interrupt

### 2.1 Address Space

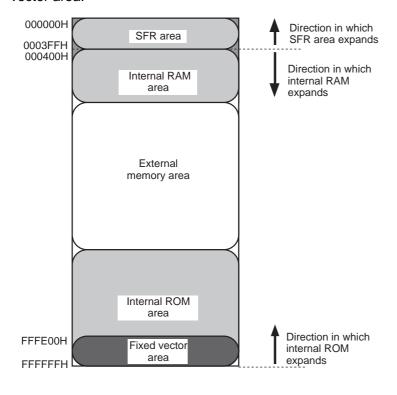

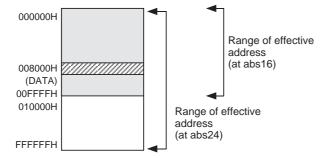

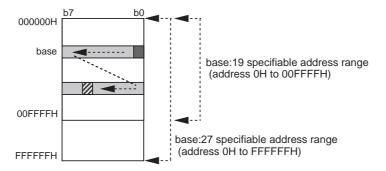

The M16C/80 series has 16 M bytes of address space ranging from address 000000H to address FFFFFH. This section explains the address space and memory mapping, the SFR area, and the fixed vector area of the M16C/80 group.

#### **Address Space**

Figure 2.1.1 shows the address space of the M16C/80 group.

Addresses 000000H to 0003FFH are the Special Function Register (SFR) area. The SFR area in each type of M16C/80 group microcomputer begins with address 0003FFH and expands toward smaller addresses.

Addresses following 000400H constitute the memory area. The memory area in each type of M16C/80 group microcomputer consists of a RAM area which begins with address 00400H and expands toward larger addresses and a ROM area which begins with address FFFFFH and expands toward smaller addresses. However, addresses FFFE00H to FFFFFHH are the fixed vector area.

Figure 2.1.1 Address space

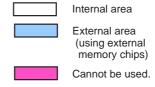

#### 2.1.1 Operation Modes and Memory Mapping

The M16C/80 group chooses one operation mode from three modes available: single-chip, memory expansion, and microprocessor modes. The M16C/80 group address space and the usable areas and memory mapping varies with each operation mode.

#### **Operation Modes and Memory Mapping**

- Single-chip mode

In this mode, only the internal areas (SFR, internal RAM, and internal ROM) can be accessed.

- Memory expansion mode

In this mode, the internal areas (SFR, internal RAM, and internal ROM) and an external memory area can be accessed.

- Microprocessor mode

In this mode, the SFR and internal RAM areas and an external memory area can be accessed.

(The internal ROM area cannot be accessed.)

Figure 2.1.2 shows the M16C/80 group memory mapping in each operation mode.

(ROM: 128 Kbytes; RAM: 10 Kbytes Example)

Figure 2.1.2 Operation modes and memory mapping

#### 2.1.2 SFR Area

A range of control registers are allocated in this area, including the processor mode register that determines the operation mode and the peripheral unit control registers for I/O ports, A-D converter, UART, and timers. For the bit configurations of these control registers, refer to the M16C/80 group data sheets and user's manuals.

The unused locations in the SFR area are reserved for the system and cannot be used by the user.

### SFR Area: Control Register Allocation (100-pin version)

Figures 2.1.3,2.1.4,2.1.5 and 2.1.6 show control register allocations in the SFR area. 006016 000116 006116 006216 00021 000316 006316 000416 Processor mode register 0 (PM0) 006416 006516 Processor mode register 1(PM1 000516 System clock control register 0 (CM0) 000616 006616 000716 System clock control register 1 (CM1) 006716 Wait control register (WCR) 000816 006816 DMA0 interrupt control register (DM0IC Address match interrupt enable register (AIER) 000916 006916 Timer B5 interrupt control register (TB5IC Protect register (PRCR) 000A16 DMA2 interrupt control register (DM1IC)

UART2 receive/ACK interrupt control register (S2RIC) 000B16 External data bus widthcontrol register (DS) 006B16 000C16 Main clock division register (MCD) 006C<sub>16</sub> Timer A0 interrupt control register (TA0IC) UART3 receive/ACK interrupt control register (S3RIC) 000E16 Watchdog timer start register (WDTS 006F16 Timer A2 interrupt control register (TA2IC) 000F16 006F16 Watchdog timer control register (WDC) UART4 receive/ACK interrupt control register (S4RIC) 00101 007016 Timer A4 interrupt control register (TA4IC) 001116 007116 Address match interrupt register 0 (RMAD0) Bus collision detection(UART3) interrupt control register (BCN3IC) 001216 007216 UART0 receive interrupt control register (S0RIC 00131 007316 A-D conversion interrupt control register (ADIC) 001416 007416 UART1 receive interrupt control register (S1RIC) 001516 Address match interrupt register 1 (RMAD1) 007516 001616 007616 Timer B1 interrupt control register (TB1IC) 001716 007716 001816 007816 Timer B3 interrupt control register (TB3IC) 001916 00791 Address match interrupt register 2 (RMAD2) INT5 interrupt control register (INT5IC) 001A16 007A<sub>16</sub> 001B16 007B16 001C16 007C16 INT3 interrupt control register (INT3IC) Address match interrupt register 3 (RMAD3) 001D16 007D16 001E16 007E16 INT1 interrupt control register (INT1IC) 001F16 007F1 00201 00801 002116 Emulator interrupt vector table register (EIAD) \* 008116 00221 008216 Emulator interrupt detect register (EITD) \* 002316 008316 002416 Emulator protect register (EPRR) \* 00841 00251 008516 008616 00271 00871 00281 008816 DMA1 interrupt control register (DM1IC) 00291 UART2 transmit/NACK interrupt control register (S2TIC) 002A1 008816 DMA3 interrupt control register (DM3IC) 002B1 008B16 UART3 transmit/NACK interrupt control register (S3TIC) 002C Timer A1 interrupt control register (TA1IC) 002D1 008D16 UART4 transmit/NACK interrupt control register (S4TIC) 002E1 008E16 Timer A3 interrupt control register (TA3IC) 002F1 Bus collision detection(UART2) interrupt control register (BCN2IC) 003016 ROM areaset register (ROA) \* 009016 UART0 transmit interrupt control register (S0TIC) Debug monitor area set register (DBA) \*

Expansion area set register 0 (EXA0) \* 003116 009116 Bus collision detection(UART4) interrupt control register (BCN4IC) 003216 009216 UART1 transmit interrupt control register (S1TIC) 003316 Expansion area set register 1 (EXA1) \* 009316 Key input interrupt control register (KUPIC) Expansion area set register 2 (EXA2) Timer B0 interrupt control register (TB0IC) 003516 Expansion area set register 3 (EXA3) \* 009516 00361 009616 Timer B2 interrupt control register (TB2IC) 00371 00971 00381 009816 Timer B4 interrupt control register (TB4IC) 00391 00991 003A1 009A<sub>16</sub> INT4 interrupt control register (INT4IC) 003B1 009B16 003C1 009C16 INT2 interrupt control register (INT2IC) 009D16 003D1 003E1 009E16 INTO interrupt control register (INTOIC) 009F<sub>16</sub> Exit priority register (RLVL) 00A016 004016 DRAM control register (DRAMCONT) 004116 00A116 DRAM reflesh interval set register (REFCNT) 00A216 00431 00A316 00A416 \*As this register is used exclusively for debugger purposes, user cannot use this. Do not access to the register.

Figure 2.1.3 Control register allocation 1

Figure 2.1.4 Control register allocation 2

12

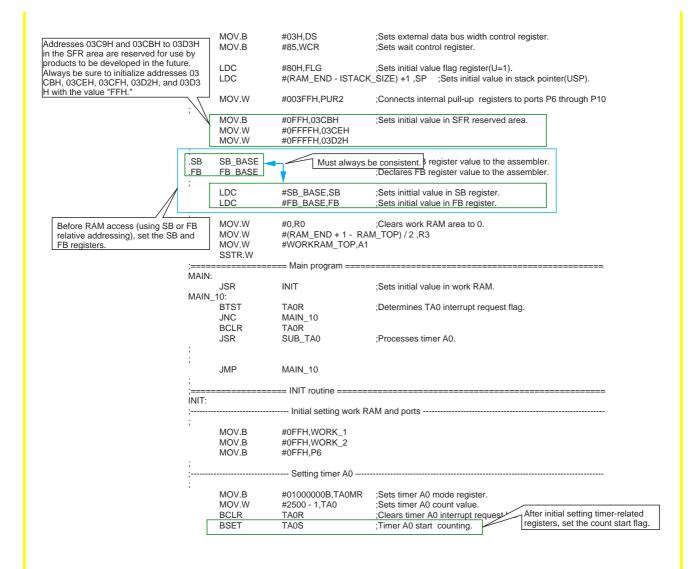

Note: Address 03C9H, 03CBH to 03D3H area is for future plan.

Must set "FF16" to address 03CBH, 03CEH, 03CFH, 03D2H, 03D3H at initial setting.

Figure 2.1.6 Control register allocation 4

#### **Determination of Operation Mode**

The operation modes of the M16C/80 group are determined by the CNVSS pin, processor mode register 0 (address 000004H), and bits 0 and 1.

Figure 2.1.7 shows the configuration of processor mode register 0.

Processor mode register 0 (Note 1)

- Note 1: Set bit 1 of protect register (address 000A<sub>16</sub>) to "1" when writeing new value to this register.

- Note 2: If the Vcc voltage is applied to the CNVss, the value of this register when reset when reset is 0316. ( PM00 is set to "1" and PM07 is set to "0".)

- Note 3: Valid in microprocessor and memory expansion modes 1,2 and 3.Do not use multiplex bus when mode 0 is selected. Do not set to allocated to CS2 space when mode 2 is selected.

- Note 4: After the reset has been released the M16C/80 group MCU operates using the separate bus. As a result,in microprocessor mode,you cannot select the full CS space multiplex bus. When you select the full CS space multiplex bus in memory expansion mode, the address bus operates with 64 K bytes boundance for each chip select.

Mode 0 : Multiplexed bus cannot be used.

Mode 1: CS0 to CS2 when you select full CS space. Mode 2: CS0 to CS1 when you select full CS space. Mode 3: CS0 to CS3 when you select full CS space.

Note 5 : No BCLK is output in single chip mode even when "0" is set in PM07. When stopping clock output in microprocessor or memory expansion mode, make the following settings: PM07="1", bit 0 ( CM00 ) and bit 1 (CM01) of system clock control register 0 = "0". "L" is now output from P52.

Note 6: See the data sheet for BCLK.

Note 7: When using 16-bit bus width in DRAM controler, set this bit to "1".

Figure 2.1.7 Processor mode register 0

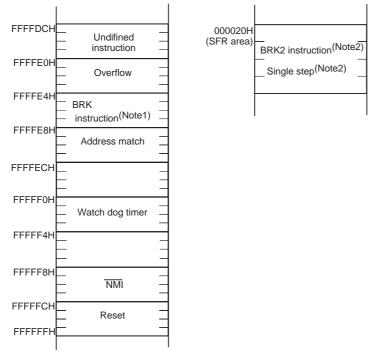

#### 2.1.3 Fixed Vector Area

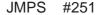

The M16C/80 group fixed vector area consists of addresses FFFE00H to FFFFFH. Addresses FFFE00H to FFFFDBH in this area constitute a special page vector table. This table is used to store the start addresses of subroutines and jump addresses, so that subroutine call and jump instructions can be executed using two bytes, helping to reduce the number of program steps. Addresses FFFFDCH to FFFFFH in the fixed vector area constitute a fixed interrupt vector table for reset and NMI. This table is used to store the start addresses of interrupt routines. An interrupt vector table for timer interrupts, etc. can be set at any desired address by an internal register (INTB). For details, refer to the section dealing with interrupts in Chapter 4.

#### **Memory Mapping in Fixed Vector Area**

### 2.2 Register Set

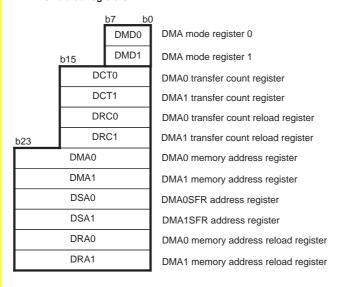

The following explains the general registers, high-speed interrupt registers, and DMAC-related registers included in the M16C/80 series CPU core.

#### **Register Structure**

Figure 2.2.1 shows the register structure of the M16C/80 series CPU core. Eight registers--R0, R1, R2, R3, A0, A1, FB, and SB--are available in two sets each. The following shows the function of each register.

#### **General registers**

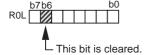

(1) Data registers (R0, R1, R2, and R3)

These registers consist of 16 bits each and are used mainly for data transfer and arithmetic/logic operations.

Registers R0 and R1 can be used separately for upper bytes (R0H, R1H) and lower bytes (R0L, R1L) as 8-bit data registers. For some instructions, registers R2 and R0 and registers R3 and R1 can be combined for use as 32-bit data registers (R2R0, R3R1), respectively.

(2) Address registers (A0 and A1)

These registers consist of 24 bits, and have the functions equivalent to those of the data registers. In addition, these registers are used in address register indirect addressing and address register relative addressing.

(3) Frame base register (FB)

This register consists of 24 bits, and is used in FB relative addressing.

(4) Static base register (SB)

This register consists of 24 bits, and is used in SB relative addressing.

(5) Program counter (PC)

This counter consists of 24 bits, indicating the address of an instruction to be executed.

(6) Interrupt table register (INTB)

This register consists of 24 bits, indicating the start address of an interrupt vector table.

(7) Stack pointers (USP or ISP)

There are two stack pointers: a user stack pointer (USP) and an interrupt stack pointer (ISP). Both of these pointers consist of 24 bits.

The stack pointers used (USP or ISP) are switched over by a stack pointer select flag (U flag). The U flag is assigned to bit 7 of the flag register (FLG).

Set odd numbers in USP and ISP. Execution efficiency is better when odd numbers are set.

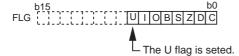

(8) Flag register (FLG)

This register consists of 11 bits, each of which is used as a flag.

#### **High-speed interrupt registers**

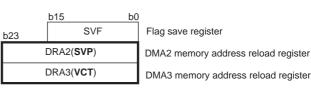

(9) Save flag register (SVF)

This register consists of 16 bits and is used to save the flag register when a high-speed interrupt is generated.

#### (10) Save PC register (SVP)

This register consists of 24 bits and is used to save the program counter when a high-speed interrupt is generated.

#### (11) Vector register (VCT)

This register consists of 24 bits and is used to indicate the jump address when a high-speed interrupt is generated.

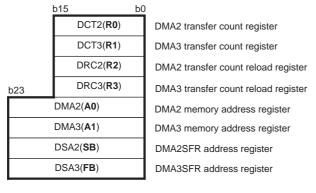

#### **DMAC** related registers

(12) DMA mode registers (DMD0 and DMD1)

These registers consist of 8 bits and are used to set the transfer mode, etc. for DMA.

(13) DMA transfer count registers (DCT0 and DCT1)

These registers consist of 16 bits and are used to set the number of DMA transfers performed.

(14) DMA transfer count reload registers (DRC0 and DRC1)

These registers consist of 16 bits and are used to reload the DMA transfer count registers.

(15) DMA memory address registers (DMA0 and DMA1)

These registers consist of 24 bits and are used to set a memory address at the source or destination of DMA transfer.

(16) DMA SFR address registers (DSA0 and DSA1)

These registers consist of 24 bits and are used to set a fixed address at the source or destination of DMA transfer.

(17) DMA memory address reload registers (DRA0 and DRA1)

These registers consist of 24 bits and are used to reload the DMA memory address registers.

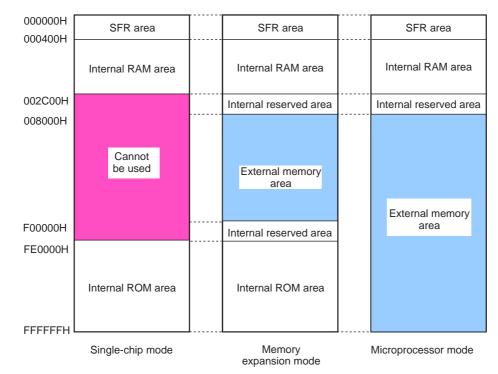

#### Flag Register (FLG)

Figure 2.2.2 shows the bit configuration of the flag register (FLG). The function of each flag is described below.

#### • Bit 0: Carry flag (C flag)

This bit holds a carry or borrow that has occurred in an arithmetic/logic operation or a bit that has been shifted out.

#### • Bit 1: Debug flag (D flag)

This flag enables a single-step interrupt.

When this flag is 1, a single-step interrupt is generated after instruction execution. When the interrupt is accepted, this flag is cleared to 0.

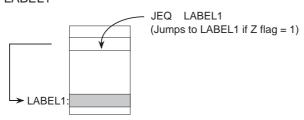

#### • Bit 2: Zero flag (Z flag)

This flag is set to 1 when the operation resulted in 0; otherwise, the flag is 0.

#### • Bit 3: Sign flag (S flag)

This flag is set to 1 when the operation resulted in an negative number. The flag is 0 when the result is positive.

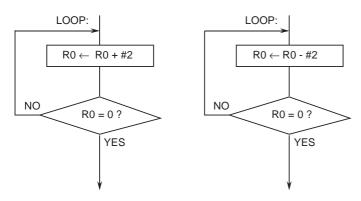

#### • Bit 4: Register bank specifying flag (B flag)

This flag chooses a register bank. Register bank 0 is selected when the flag is 0. Register bank 1 is selected when the flag is 1.

#### • Bit 5: Overflow flag (O flag)

This flag is set to 1 when the operation resulted in an overflow.

#### • Bit 6: Interrupt enable flag (I flag)

This flag enables a maskable interrupt.

The interrupt is enabled when the flag is 1, and is disabled when the flag is 0. This flag is cleared to 0 when the interrupt is accepted.

#### • Bit 7: Stack pointer specifying flag (U flag)

The user stack pointer (USP) is selected when this flag is 1. The interrupt stack pointer (ISP) is selected when the flag is 0.

This flag is cleared to 0 when a hardware interrupt is accepted or an INT instruction of software interrupt numbers 0 to 31 is executed.

#### • Bits 8 to 11: Reserved.

#### • Bits 12 to 14: Processor interrupt priority level (IPL)

The processor interrupt priority level (IPL) consists of three bits, for specification of up to eight processor interrupt priority levels from level 0 to level 7.

If the priority level of a requested interrupt is greater than the processor interrupt priority level(IPL), the interrupt is enabled.

#### • Bit 15: Reserved.

20

## Register Status after Reset is Cleared

Table 2.2.1 lists the status of each register after a reset is cleared (Note).

Table 2.2.1 Register Status after Reset Cleared

| Register name                                 | Status after a reset is cleared |

|-----------------------------------------------|---------------------------------|

| Data register(R0/R1/R2/R3)                    | 0000H                           |

| Address register(A0/A1)                       | 000000H                         |

| Static base register(SB)                      | 000000H                         |

| Flame base register(FB)                       | 000000H                         |

| Interrupt table register(INTB)                | 000000H                         |

| User stack pointer(USP)                       | 000000H                         |

| Interrupt stack pointer(ISP)                  | 000000H                         |

| Flag register(FLG)                            | 0000H                           |

| DMA mode register(DMD0/DMD1)                  | 00H                             |

| DMA transfer count register(DCT0/DCT1)        | Undefined.                      |

| DMA transfer count reload register(DRC0/DRC1) | Undefined.                      |

| DMA memory address register(DMA0/DMA1)        | Undefined.                      |

| DMA SFR address register(DSA0/DSA1)           | Undefined.                      |

| DMA memory address reload register(DRA0/DRA1) | Undefined.                      |

Note: For the control register status in the SFR area after a reset is cleared, refer to the M16C/80 group data sheets and user's manuals.

## 2.3 Data Types

There are four data types handled by the M16C/80 series: integer, decimal (BCD), string, and bit. This section describes these data types.

#### Integer

## **Decimal (BCD)**

The BCD code is handled in packed format.

This type of data can be used in four kinds of decimal arithmetic instructions: DADC, DADD, DSBB, and DSUB.

Figure 2.3.2 Decimal data

#### String

A string is a block of data comprised of a consecutive number of 1-byte or 1-word (16-bit) data. This type of data can be used in seven kinds of string instructions:SMOVB,SMOVF,SSTR,SCMPU,SIN and SOUT.

Figure 2.3.3 String data

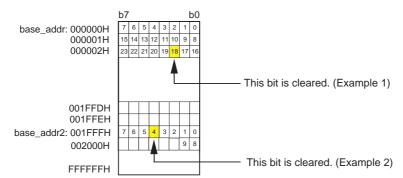

#### Bit

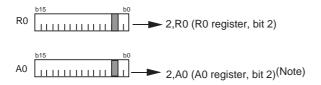

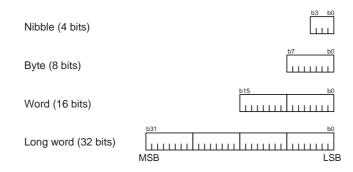

Bit can be used in 14 kinds of bit instructions, including BCLR, BSET, BTST, and BNTST. Bits in each register are specified by a register name and a bit number, 0 to 15. Memory bits are specified by a different method in a different range depending on the addressing mode used. For details, refer to Section 2.5.4, "Bit Instruction Addressing".

Figure 2.3.4 Specification of register bits

Figure 2.3.5 Specification of memory bits

Note: A0 and A1 register can be specified by the lower 8 bit.

## 2.4 Data Arrangement

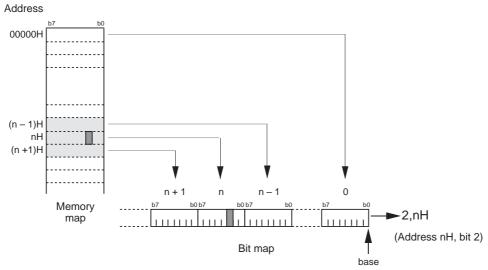

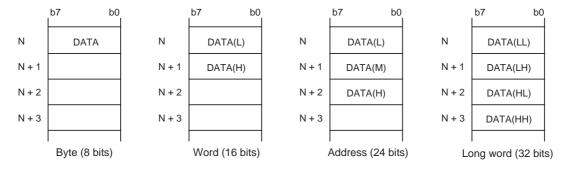

The M16C/80 series can handle nibble (4-bit) and byte (8-bit) data efficiently. This section explains the data arrangements that can be handled by the M16C/80 series.

## **Data Arrangement in Register**

Figure 2.4.1 shows the relationship between the data sizes and the bit numbers of a register. As shown below, the bit number of the least significant bit (LSB) is 0. The bit number of the most significant bit (MSB) varies with the data sizes handled.

Figure 2.4.1 Data arrangement in register

#### **Data Arrangement in Memory**

Figure 2.4.2 shows the data arrangement in the M16C/80 series memory.

Data is arranged in memory in units of 8 bits as shown below. A word (16 bits) is divided between the lower byte and the upper byte, with the lower byte, DATA(L), placed in a smaller address location. Similarly, addresses (24 bits) and long words (32 bits) are located in memory beginning with the lower byte, DATA(L) or DATA(LL).

Figure 2.4.2 Data arrangement in memory

## 2.5 Addressing Modes

This section explains the M16C/80 series addressing.

The four types of addressing modes shown below are available.

- (1) General instruction addressing

- The entire address space from address 000000H to FFFFFH is accessed.

- (2) Indirect instruction addressing

- The entire address space from address 000000H to FFFFFH is accessed.

- (3) Special instruction addressing

- The entire address space from 000000H to FFFFFH is accessed and control registers.

- (4) Bit instruction addressing

- The entire address space from address 000000H to FFFFFH is accessed in units of bits.

## **List of Addressing Modes**

All addressing modes are summarized in Table 2.5.1 and Table 2.5.2 below.

Table 2.5.1 Addressing Modes of M16C/80 Series 1

| Item                                          | em Content                                                               |                                                     |

|-----------------------------------------------|--------------------------------------------------------------------------|-----------------------------------------------------|

| ddressing mode                                | General instruction                                                      | Indirect instruction                                |

| Immediate                                     | imm:8/16/32 bits                                                         | X                                                   |

| Register direct                               | Data register and address registers only                                 | X                                                   |

| Control register direct                       | X                                                                        | X                                                   |

| Absolute                                      | abs:16 bits (0 to FFFFH)<br>24 bits (0 to FFFFFFH)                       | Х                                                   |

| Absolute indirect                             | X                                                                        | [abs : 16/24 bits] (0 to FFFFFFH)                   |

| Address register indirect                     | [A0] or [A1] without disp                                                | X                                                   |

| Two-stage address register indirect           | X                                                                        | [[A0]] or[[A1]] without disp (0 to FFFFFH)          |

| Address register relative                     | [A0] or [A1] dsp: 8/16/24 bits                                           | X                                                   |

| Address register relative indirect            | Х                                                                        | [dsp:8/16/24[A0]] or [dsp:8/16/24[A1]] (0 to FFFFFF |

| SB relative and FB relative                   | dsp:8[SB]<br>dsp:16[SB]<br>dsp:8/16 bits(0 to 255 / 0 to 65534)          | x                                                   |

|                                               | dsp:8[FB]<br>dsp:16[FB]<br>dsp:8/16 bits(-128 to +127 / 32768 to +32767) | Х                                                   |

| SB relative indirect and FB relative indirect | X                                                                        | [dsp:8/16[SB]] (0 to FFFFFFH)                       |

|                                               | X                                                                        | [dsp:8/16[FB]] (0 to FFFFFFH)                       |

| Stack pointer relative                        | dsp:8[SP]<br>dsp:8 bits (-128 to +127) *MOV instruction only             | Х                                                   |

| Program counter relative                      | X                                                                        | X                                                   |

| FLG direct                                    | X                                                                        | X                                                   |

## Table 2.5.2 Addressing Modes of M16C/80 Series 2

| ltem Content                                  |                                                                                                                                                                                         | tent                                                                 |

|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| Addressing mode                               | Special instruction                                                                                                                                                                     | Bit instruction                                                      |

| Immediate                                     | X                                                                                                                                                                                       | X                                                                    |

| Register direct                               | X                                                                                                                                                                                       | R0L/R0H/R1L/R1H/A0/A1 only                                           |

| Control register direct                       | INTB,ISP,SP,DMD0 etc.control registeronly                                                                                                                                               | X                                                                    |

| Absolute                                      | Х                                                                                                                                                                                       | base:19/27 bits (0 to FFFFH / 0 to 0FFFFFFH)                         |

| Absolute indirect                             | X                                                                                                                                                                                       | x                                                                    |

| Address register indirect                     | Х                                                                                                                                                                                       | bit,[A0] or bit,[A1](0H to 0FFFFFFH)<br>bit:0 to 7                   |

| Two-stage address register indirect           | Х                                                                                                                                                                                       | X                                                                    |

| Address register relative                     | Х                                                                                                                                                                                       | bit,base[A0] or bit,base[A1]<br>base:11/19/27                        |

| Address register relative indirect            | Х                                                                                                                                                                                       | X                                                                    |

| SB relative and FB relative                   | X                                                                                                                                                                                       | bit,base:11[SB] (0H to FFH)<br>bit,base:19[SB] (0H to FFFFH)         |

|                                               | Х                                                                                                                                                                                       | bit,base:11[FB] (-128 to +127)<br>bit,base:19[FB] (-32768 to +32767) |

| SB relative indirect and FB relative indirect | X                                                                                                                                                                                       | X                                                                    |

|                                               | X                                                                                                                                                                                       | X                                                                    |

| Stack pointer relative                        | X                                                                                                                                                                                       | X                                                                    |

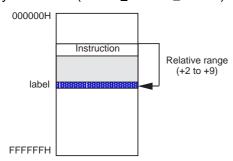

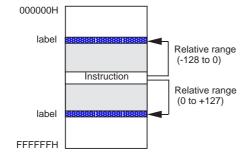

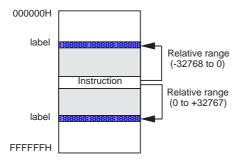

| Program counter relative                      | label: .S: +0 to +7(JMP instruction only) .B: -128 to +127(JMP,JSR instruction only) .W: -32768 to +32767(JMP,JSR instruction only) .without length: -127 to +128(Jcn instruction only) | X                                                                    |

| FLG direct                                    | X                                                                                                                                                                                       | U, I, O, B, S, Z, D, C flag *FSET,FCLR instruction on                |

#### 2.5.1 General Instruction Addressing

This section explains each addressing in the general instruction addressing mode.

#### **Immediate**

The immediate indicated by #IMM is the subject on which operation is performed. Add a # before the immediate.

Symbol: #IMM, #IMM8, #IMM16, #IMM32

Example: #123 (decimal)

#7DH (hexadecimal) #01111011B (binary)

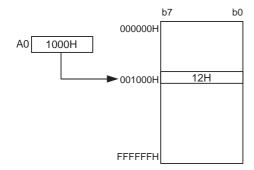

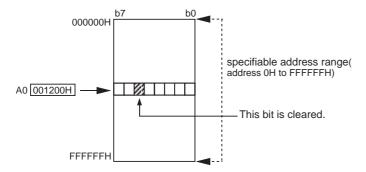

#### **Absolute**

The value indicated by abs16/24 is the effective address on which operation is performed. The range of effective addresses is 000000H to 000FFFFH at abs16, and 000000H to FFFFFH at abs24.

Symbol: abs16 or abs 24 Example: MOV.B #12H,DATA

Figure 2.5.1 Absolute addressing

#### Register direct

A specified register is the subject on which operation is performed. However, only the data and address registers can be used here.

Symbol: 8 bits R0L, R0H, R1L, R1H

16 bits R0, R1, R2, R3, A0, A1

32 bits R2R0, R3R1

## **Address Register Indirect**

The value of an address register is the effective address to be operated on. The range of effective addresses is 000000H to FFFFFH.

Symbol: [A0], [A1]

Example: MOV.B #12H, [A0]

Figure 2.5.2 Address register indirect addressing

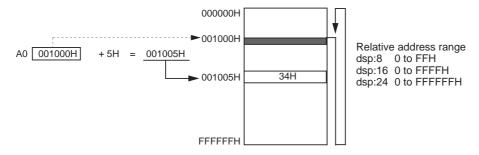

#### **Address Register Relative**

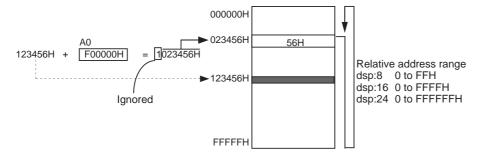

The value of an address register plus a displacement (dsp)<sup>(Note)</sup> is the effective address to be operated on. The range of effective addresses is 000000H to FFFFFH. If the addition result exceeds FFFFFH, the most significant bits above and including bit 25 are ignored and the address returns to 000000H.

Symbol: dsp:8[A0], dsp:16[A0], dsp:24[A0], dsp:8[A1],dsp:16[A1],dsp24[A1]

#### (1) When dsp is handled as a displacement

Example: MOV.B #34H,5[A0]

Figure 2.5.3 Address register relative addressing 1

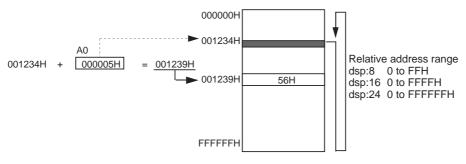

## (2) When address register (A0) is handled as a displacement

Example: MOV.B #56H,1234H[A0]

Figure 2.5.4 Address register relative addressing 2

#### (3) When the addition result exceeds 0FFFFH

Example: MOV.B #56H,1234H[A0]

Figure 2.5.5 Address register relative addressing 3

Note: The displacement (dsp) refers to a displacement from the reference address. In this manual, 8-bit dsp is expressed as dsp:8, 16-bit dsp is expressed as dsp:16, and 24-bit dsp is expressed as dsp:24.

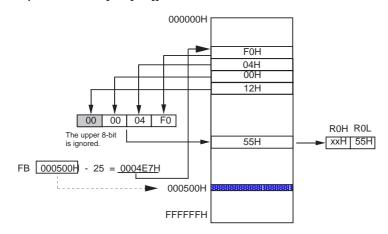

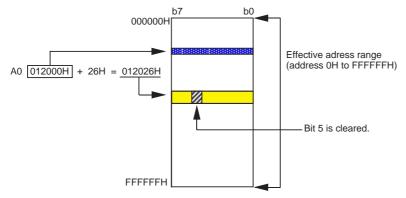

#### **SB** Relative

The address indicated by the content of static base register(SB) plus the value indicated by displacement(dsp) -added not including the sign bits- constitutes the effective address to be operated on. The range of effective addresses is 000000H to FFFFFH. However, if the addition resulted in exceeding FFFFFH ,the bits above bit 25 are ignored, and the address returns to 000000H.

Symbol: dsp:8[SB], dsp:16[SB] Example: MOV.B #12H,5[SB]

Figure 2.5.6 SB relative addressing

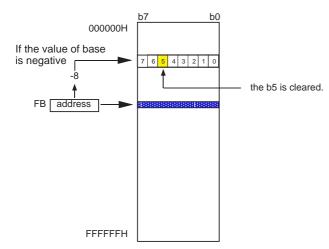

#### **FB** Relative

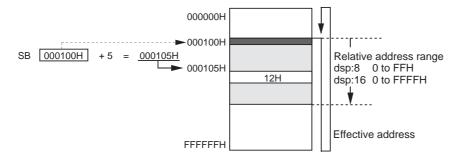

The address indicated by the content of frame base register(FB) plus the value indicated by displacement(dsp) -added not including the sign bits- constitutes the effective address to be operated on. The range of effective addresses is 000000H to FFFFFH. However, if the addition resulted in exceeding 000000H to FFFFFFH ,the bits above bit 25 are ignored, and the address returns to 000000H or FFFFFFH.

Symbol: dsp:8[FB]

# (1) When dsp is a positive value Example: MOV.B #12H,5[FB]

000000H

FB 000100H + 5 = 000105H

000105H

12H

Relative address range dsp:8 0 to +127 dsp:16 0 to +32767

Effective address

Figure 2.5.7 FB relative addressing 1

# (2) When dsp is a negative value Example: MOV.B #12H,-5[FB]

000000H

FB 000100H - 5 = 000FFBH

000FFBH 12H

001000H

Relative address range dsp:8 -128 to 0 dsp:16 -32768 to 0

Effective address

Figure 2.5.8 FB relative addressing 2

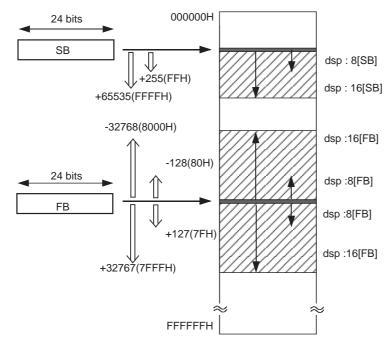

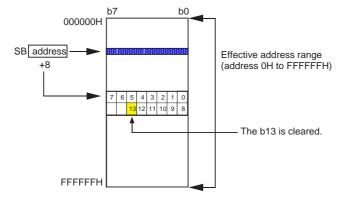

#### Column Difference between SB Relative and FB Relative

In SB relative addressing, the address indicated by the SB register content and the value indicated by dsp are added not including the sign and the result of addition is the effective address to be operated on. The relative range is 0 to +255 (FFH) for dsp: 8[SB], and 0 to +65535 (FFFFH) for dsp: 16[SB].

In FB relative addressing, dsp is added to or subtracted from the address indicated by the FB register content and the result of addition or subtraction is the effective address to be operated on. The relative range is -128 to +127 (80H to 7FH) for dsp: 8[FB], and -32768 to +32767 (8000H to 7FFFH) for dsp: 16[FB]. FB relative allows accessing memory locations in the negative direction. The dsp used for this addressing can be 8 bits or 16 bits.

Figure 2.5.9 SB relative and FB relative addressing

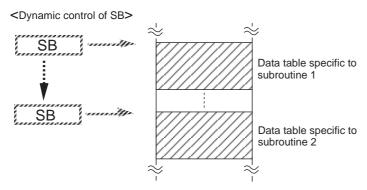

#### Column Application Example of SB Relative

SB relative addressing can be applied for the specific data table of each subroutine as shown in Figure 2.5.10. Although the data necessary to run each subroutine must be switched over when calling the subroutine, use of SB relative addressing helps to accomplish this switchover by only rewriting the SB register.

Figure 2.5.10 Application example of SB relative addressing

#### Column Application Example of FB Relative

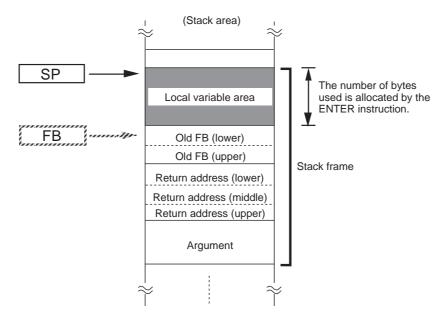

FB relative addressing can be used for the stack frame that is created when calling a function, as shown in Figure 2.5.11. Since the local variable area in the stack frame is located in the negative direction of addresses, FB relative addressing is needed because it allows for access in both positive and negative directions from the base.

<a>Accessing local variable area></a>

Figure 2.5.11 Application example of FB relative addressing

#### **Stack Pointer Relative (SP Relative)**

In SP relative addressing, the address indicated by the SB register content and the value indicated by dsp are added including the sign and the result of addition is the effective address to be operated on. SP relative addressing can only be used in the MOV instruction. The range of effective addresses is 000000H to FFFFFFH. If the result of addition exceeds the range of 000000H to FFFFFFH, any value above 25 bits is ignored and the address wraps around to 000000H or FFFFFFH.

Symbol: dsp:8[SP]

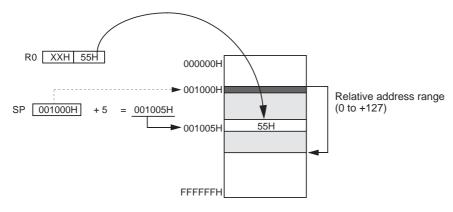

#### (1) When dsp is a positive value

Example: MOV.B R0L,5[SP]

Figure 2.5.12 SP relative addressing 1

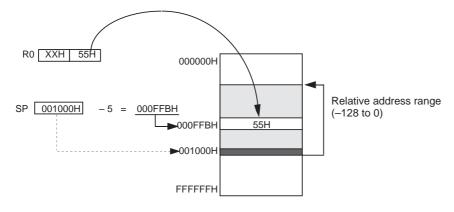

## (2) When dsp is a negative value

Example: MOV.B R0L,-5[SP]

Figure 2.5.13 SP relative addressing 2

## Column Relative Address Ranges of Relative Addressing

The relative address ranges of relative addressing are summarized in Table 2.5.3.

Table 2.5.3 Relative Address Ranges of Relative Addressing

| Addressing mode                | Descriptive form                                   | Relative range                                                                                   |

|--------------------------------|----------------------------------------------------|--------------------------------------------------------------------------------------------------|

| Address register relative      | dsp:8[An]<br>dsp:16[An]<br>dsp:24[An]              | 0 to 255(FFH)<br>0 to 65535(FFFFH)<br>0 to 16777215(FFFFFFH)                                     |

| SB relative<br>and FB relative | dsp:8[SB]<br>dsp:16[SB]<br>dsp:8[FB]<br>dsp:16[FB] | 0 to 255(0FFH)<br>0 to 65535(0FFFFH)<br>-128(80H) to +127(7FH)<br>-32768(8000H) to +32767(7FFFH) |

| Stack pointer relative         | dsp:8[SP]                                          | -128(80H) to +127(7FH)                                                                           |

#### 2.5.2 Indirect instruction Addressing

The Indirect instruction addressing accesses an area from address 000000H to FFFFFH. This section explains each addressing in the indirect instruction addressing mode.

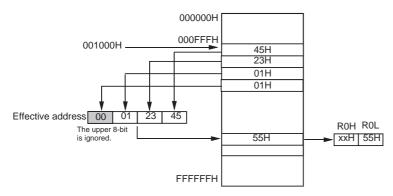

#### **Absolute indirect**

The 4-bytes value indicated by absolute addressing constitutes the effective address to be operated on. The effective address range is 000000H to FFFFFH.

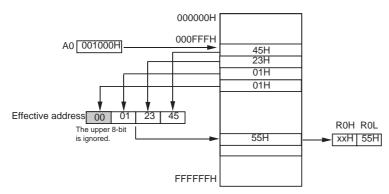

Symbol: [abs16] or [abs24] Example: MOV.B [001000H],R0L

Figure 2.5.14 Absolute indirect addressing

## Two-stage address register indirect

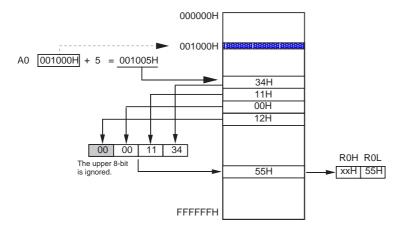

The 4-bytes value indicated by address register(A0/A1) indirect constitutes the effective address to be operated on. The effective address range is 000000H to FFFFFFH.

Symbol: [[A0]] or [[A1]] Example: MOV.B [[A0]],R0L

Figure 2.5.15 Two-stage address register indirect addressing

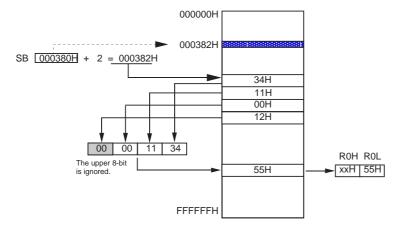

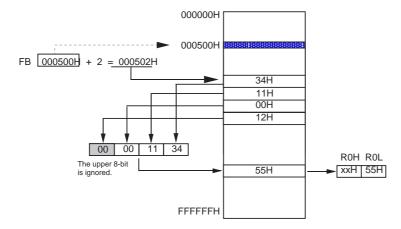

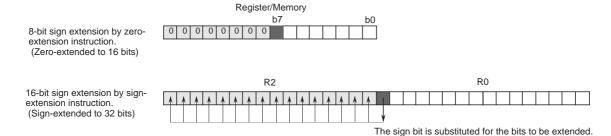

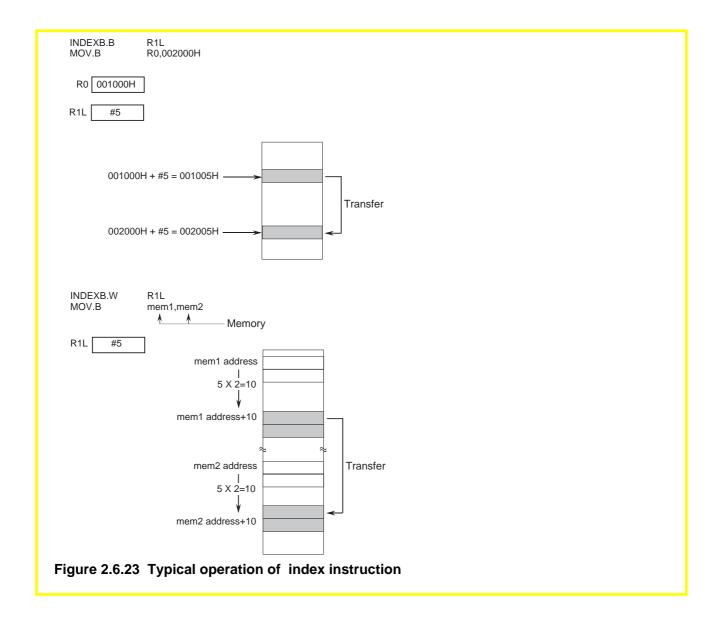

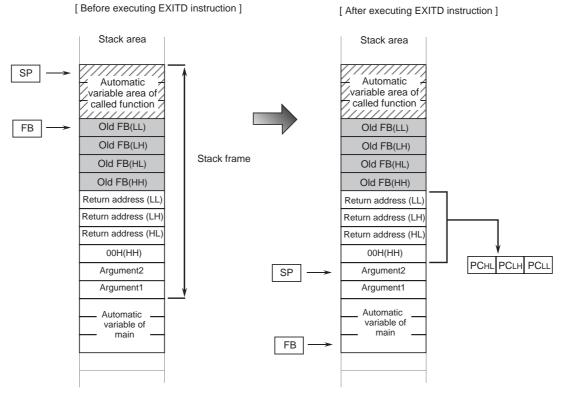

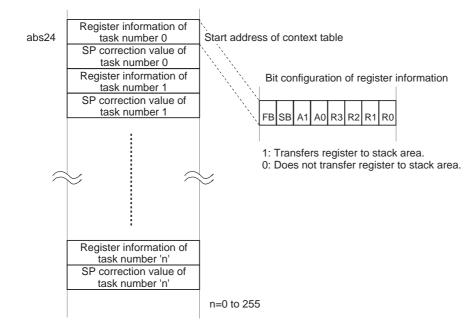

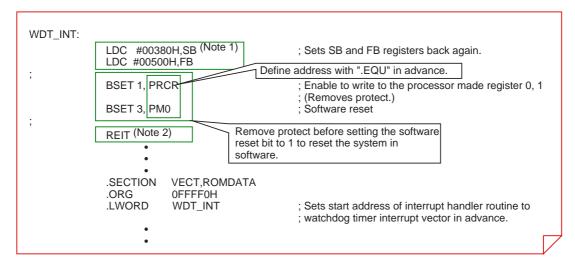

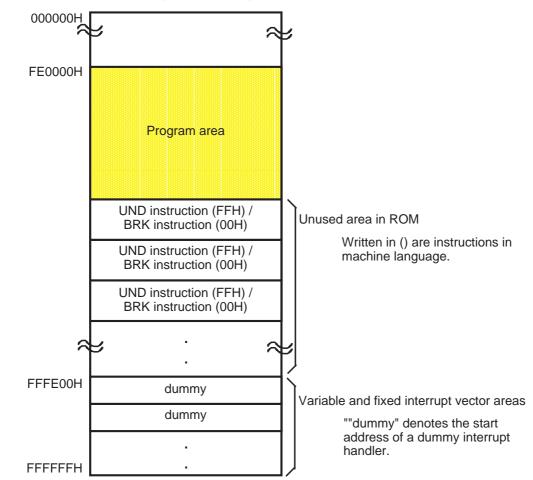

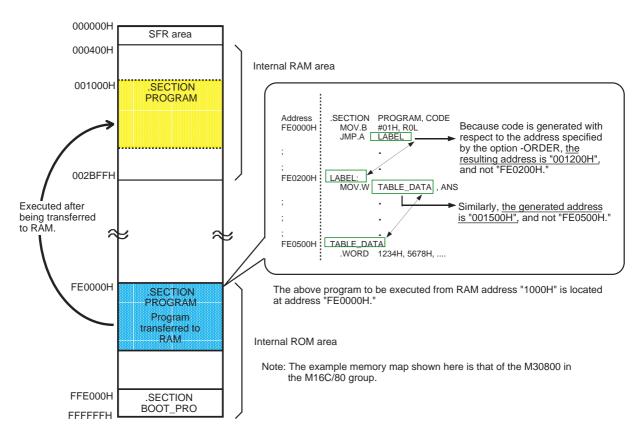

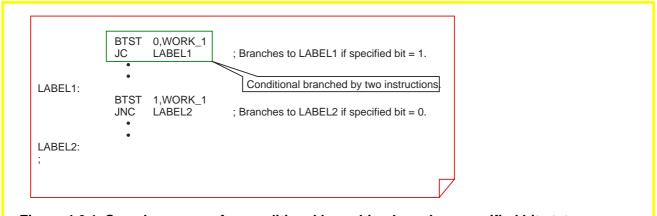

#### Address register relative indirect