|       | <b>A</b> |

|-------|----------|

| GRADE |          |

| URADE | . A      |

|       | / \      |

# MESC TECHNICAL NEWS No. M7700-65-9912

## Corrections and Supplementary Explanation for "7733/7735/7736 Group User's Manual" (REV. B)

This news includes a few corrections and supplementary explanation for "7733/7735/ 7736 Group User's Manual".

And also, this news includes the information previously announced by the MESC TECH-NICAL NEWS (No. M7700-37-9803, Corrections and Supplementary Explanation for "7733/ 7735/7736 Group User's Manual" REV. A).

**Notes 1:** ★ represents the new information.

2: \* represents the information corrected only in the PDF version, not in the printed version (No. H-EF490-A) .

As previously announced by the MESC TECHNICAL NEWS (No. M7700-40-9809), the specifications of the 7733/7735/7736 Group MCUs have been revised. The revised points for the 7733/ 7735/7736 Group User's Manual are described on the last three pages of this news. For details of this revision, please refer to the MESC TECHNICAL NEWS, No. M7700-40-9809.

The information about the product expansion, electrical characteristics, and development support tools will not be announced by the MESC TECHNICAL NEWS, even if the above information is updated.

So, for the product expansion, electrical characteristics, and development support tools, please refer to the latest version of the following documents in our web site:

- Product Expansion

- Mitsubishi Microcomputers General Catalog\*

- Electrical Characteristics

- Datasheets

- Development Support Tools

- Datasheets

Microcomputers Development Support Tools Catalog\*

Microcomputers Development Support Tools Accessory Guide

#### Please Visit Our Web Site.

- Mitsubishi MCU Technical Information (http://www.infomicom.mesc.co.jp/indexe.htm)

- Mitsubishi Microcomputer Development Support Tools (http://www.tool-spt.mesc.co.jp/index\_e.htm)

- \* The printed version is also released.

- Notes 3: For products not included in the above web site, refer to "1996 MITSUBISHI SEMICONDUCTORS DATA BOOK (SINGLE-CHIP 16-BIT MICROCOMPUTERS) Vol. 1 to 2."

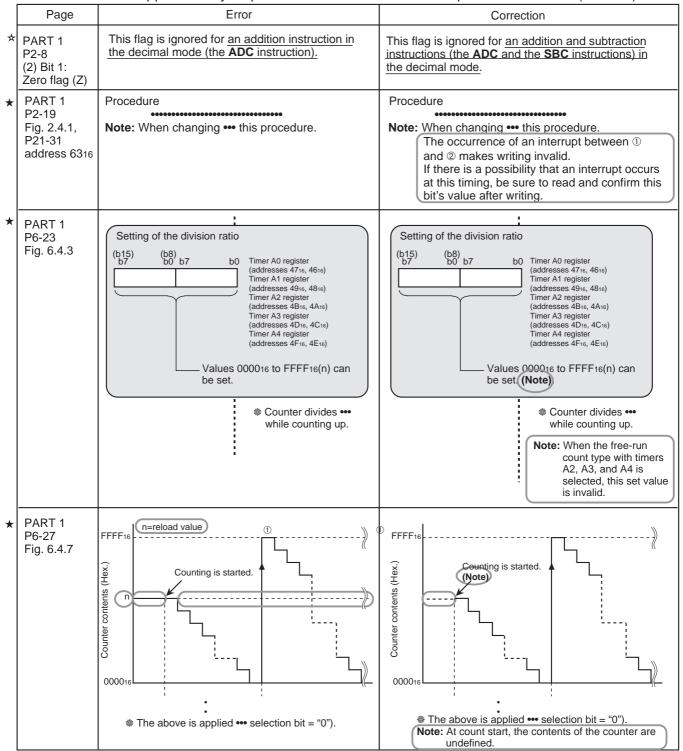

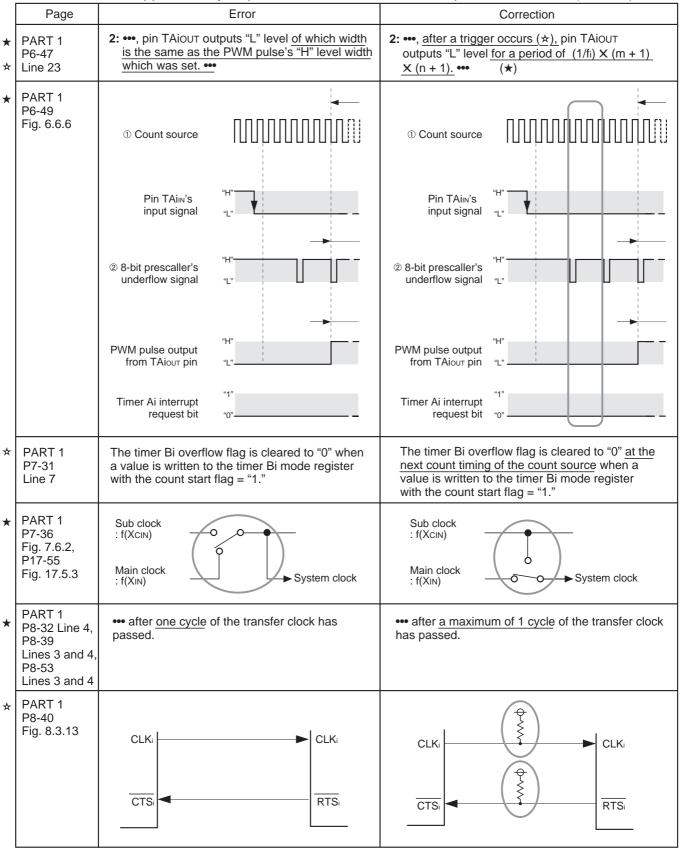

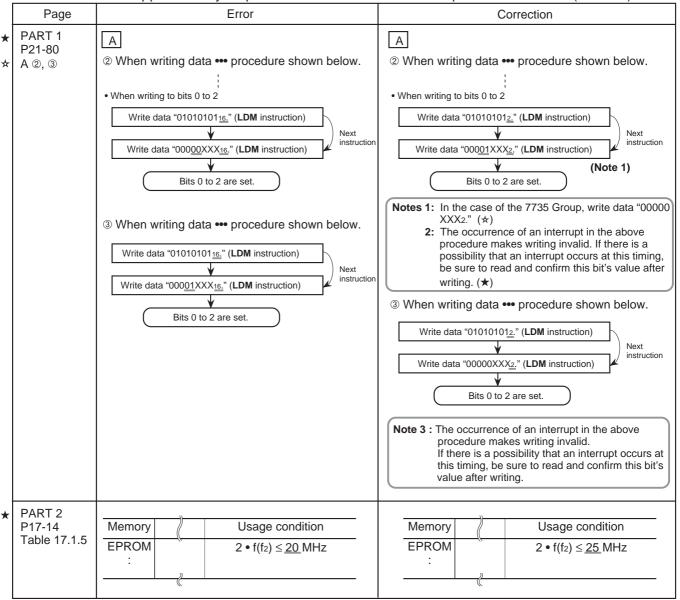

|   |                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                     | Toolog Group Gool o Mariaar (1121: 5) 110: 0                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|   | Page                                                                                                                                                                                                                                                                                                | Error                                                                                                                                                                                                                                                                                                                                               | Correction                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| * | PART 1<br>P8-46<br>Table 8.4.4                                                                                                                                                                                                                                                                      | 14400 f <sub>2</sub> 52(3F <sub>16</sub> ) 14490.57 53(40 <sub>16</sub> ) 14467.59                                                                                                                                                                                                                                                                  | 14400 f <sub>2</sub> 52(34 <sub>16</sub> ) 14490.57 53(35 <sub>16</sub> ) 14467.59                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| * | PART 1<br>P8-59<br>Line 2                                                                                                                                                                                                                                                                           | And then, reception is started when ST is detected.                                                                                                                                                                                                                                                                                                 | And then, the transfer clock is generated when ST is detected, and reception is started.                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| * | PART 1<br>P8-59<br>Fig. 8.4.11                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| * | PART 1<br>P8-60<br>Fig. 8.4.12                                                                                                                                                                                                                                                                      | Transfer clock                                                                                                                                                                                                                                                                                                                                      | Transfer clock  The transfer clock is generated at the                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|   |                                                                                                                                                                                                                                                                                                     | Reception is started at the falling edge of start bit.                                                                                                                                                                                                                                                                                              | falling edge of start bit, and reception is started.                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| * | PART 1<br>P8-62<br>Line 20                                                                                                                                                                                                                                                                          | ⑤ For the slave microcomputer whose address matches bits 6 to 0 in the receive data, <u>clear</u> the sleep mode. (Do not terminate the sleep mode for the other slave microcomputers.)                                                                                                                                                             | ⑤ For the slave microcomputer whose address matches bits 6 to 0 in the receive data, terminate the sleep mode. (Do not terminate the sleep mode for the other slave microcomputers.)                                                                                                                                                                                                                                                            |  |  |  |  |

| * | PART 1<br>P10-9<br>Fig. 10.2.3,<br>P11-5<br>Fig. 11.2.4,<br>P14-9<br>Fig. 14.3.4,<br>P21-36<br>(When writing ••),<br>PART 2<br>P10-3<br>Fig. 10.2.3,<br>P11-3<br>Fig. 11.2.4,<br>P14-3<br>Fig. 14.3.4,<br>PART3<br>P20-11 for<br>PDF version,<br>P20-10 for<br>printed version<br>(When writing ••) | (Under Figure)                                                                                                                                                                                                                                                                                                                                      | (Under Figure)  Note: The occurrence of an interrupt in the above procedure makes writing invalid.  If there is a possibility that an interrupt occurs at this timing, be sure to read and confirm this bit's value after writing.                                                                                                                                                                                                              |  |  |  |  |

| * | DADT 4                                                                                                                                                                                                                                                                                              | 4. When the <b>STP</b> instruction (Refer to chapter "11. <b>STOP AND WAIT MODES</b> ") is executed, the watchdog timer stops operating. For the system where the watchdog timer is used to detect a program runaway, <u>select</u> " <b>STP</b> instruction disabled" with " <b>STP</b> instruction option" on "MASK ROM ORDER CONFIRMATION FORM." | 4. When the STP instruction (refer to "CHAPTER 11. STOP AND WAIT MODES") is executed, the watchdog timer stops operating. Unexpected execution of the STP instruction code (DB16) owing to a program runaway causes Watchdog timer to stop. Therefore, when Watchdog timer is used to detect a program runaway, we recommend the user to select "STP instruction disabled" with "STP instruction option" on "MASK ROM ORDER CONFIRMATION FORM." |  |  |  |  |

|   | Page                                                                   | Error                                                                                                                                           |                                                                          |                                                                                                        | Correction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                             |                                                                                                   |  |  |

|---|------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------|--|--|

| * | PART 1<br>P11-10<br>Lines 10, 11                                       |                                                                                                                                                 | fter ••• MSB becomes<br>ve no need to be acc                             |                                                                                                        | priority after ••• MSB becomes "0." (When the level sense of an INTi interrupt is used, an interrupt request is not retained. Therefore, if the level at the INTi pin is invalid when the watchdog timer's MSB becomes "0," the interrupt request is not accepted.) For interrupts which have no need to be accepted, •••                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                             |                                                                                                   |  |  |

| * | PART 1<br>P11-17<br>Table 11.4.3                                       | Interrupt                                                                                                                                       | Conditions for each function w<br>when clocks f2 and f612 are<br>stopped | hich generates interrupt request<br>when clocks f <sub>2</sub> and f <sub>512</sub> are<br>not stopped | Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | when clocks f <sub>2</sub> and f <sub>512</sub> are stopped | which generates interrupt request when clocks f <sub>2</sub> and f <sub>512</sub> are not stopped |  |  |

|   |                                                                        | A-D conversion interrupt                                                                                                                        | Disabled                                                                 | Enabled                                                                                                | A-D conversion interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Disabled                                                    | Enabled in one-shot mode and single sweep mode                                                    |  |  |

| * | PART 1<br>P17-43<br>Lines 1, 2                                         | instruct<br>operati<br>timer, <u>s</u><br>instruct                                                                                              | tion is executed, the ring. For systems which                            | n disabled" with "STP                                                                                  | instruction is executed, the watchdog timer stops operating. <u>Unexpected execution of the <b>STP</b></u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                             |                                                                                                   |  |  |

| * | PART 1<br>P21-69<br>5. Setup for<br>I/O ports<br><software></software> | <ul> <li>Read the data of •••equal.</li> <li>Periodically rewrite data •••, due to noise.</li> <li>Rewrite data to ••• periodically.</li> </ul> |                                                                          |                                                                                                        | <ul> <li>● Read the data of ••• are equal.</li> <li>● Periodically rewrite (Note) data •••, due to noise.</li> <li>● Rewrite (Notes 1, 2) data to ••• periodically.</li> <li>Notes 1: Be sure to use the LDM or STA instruction for the above rewriting.</li> <li>2: Rewrite the direction registers of ports P4–P8, P9, and P10 as follows: <ul> <li>(1) Disable interrupts with the SEI instruction, etc.</li> <li>(2) Write dummy data to addresses 1A₁6 and 1B₁6 (when rewriting an even address, write data to address 1A₁6; when an odd address, write to address 1B₁6).</li> <li>(3) Rewrite the targeted direction register.</li> </ul> </li> <li>(Refer to Technical News No. 7700-48-9906 for details of Note 2 and a program example.)</li> </ul> |                                                             |                                                                                                   |  |  |

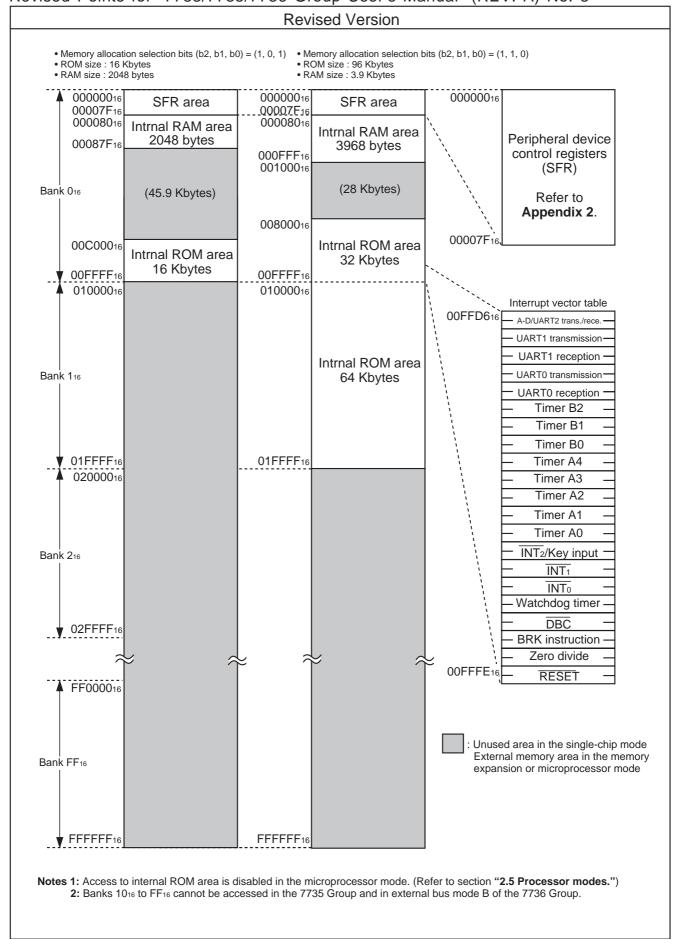

Revised Points for "7733/7735/7736 Group User's Manual" (REV. A) No. 1

|     | Page                                        | Previous Version                                      |                                                                |             | Revised Version                                                                |                         |               |                                                        |                 |

|-----|---------------------------------------------|-------------------------------------------------------|----------------------------------------------------------------|-------------|--------------------------------------------------------------------------------|-------------------------|---------------|--------------------------------------------------------|-----------------|

| ☆   | PART 1                                      |                                                       |                                                                | Functions   |                                                                                |                         |               |                                                        |                 |

|     | Page 2-21<br>Fig. 2.4.1,                    | +                                                     | Functions                                                      | <del></del> | _                                                                              | Functions               |               |                                                        |                 |

|     | PART 1                                      | 0 0 0 : 124                                           | ROM size (addresses)<br>K (001000 <sub>16</sub> to 01FFF       |             |                                                                                | 0 : 124                 |               | RAM size<br>3968 bytes                                 |                 |

|     | Page 21-30                                  | 0 0 1 : 120<br>0 1 0 : Dor                            | K (002000 <sub>16</sub> to 01FFF)<br>not select.               | F16)        | 0 1                                                                            | ) 1 : 120<br>  0 : 60 k | (bytes.       | 3968 bytes<br>2048 bytes                               |                 |

|     |                                             | 0 1 1 : Dor<br>1 0 0 : Dor                            |                                                                |             |                                                                                | l 1 : Dor<br>) 0 : 32 k |               | t.<br>2048 bytes                                       |                 |

|     |                                             | 1 0 1 : Dor                                           | 1 0 1 : 16 Kbytes. 2048 bytes<br>1 1 0 : 96 Kbytes, 3968 bytes |             |                                                                                |                         |               |                                                        |                 |

|     |                                             | 1 1 1 : 32 k                                          | 1 1 1 : Do not select.                                         |             |                                                                                |                         |               |                                                        |                 |

|     |                                             |                                                       |                                                                |             |                                                                                |                         |               |                                                        |                 |

|     |                                             |                                                       |                                                                |             |                                                                                |                         |               |                                                        |                 |

|     |                                             | Notes 1: ••• 2: When changing these bits, this change |                                                                |             | Notes 1: •••                                                                   |                         |               |                                                        |                 |

|     |                                             | must be                                               | performed in an area was COM area before and a                 | hich is     | 2: When changing these bits, this change must be performed in an area which is |                         |               |                                                        |                 |

|     |                                             | change,                                               | for example addresses                                          | 00800016    | internal ROM area before and after this change, for example addresses 00C00016 |                         |               |                                                        |                 |

|     |                                             | bits, be s                                            | F <sub>16</sub> . Also, when chang ure to follow the proce-    |             |                                                                                |                         |               |                                                        |                 |

|     |                                             |                                                       | 7733S4BFP, M37733                                              |             | 3:                                                                             |                         |               | ed only to the                                         |                 |

|     |                                             |                                                       | S4BFP, or M37735S4L<br>address 6316 is disabl                  |             | M37733MHBXXXFP. For the other microcomputers, please refer to the latest       |                         |               |                                                        |                 |

|     |                                             |                                                       |                                                                |             | datasheets.                                                                    |                         |               |                                                        |                 |

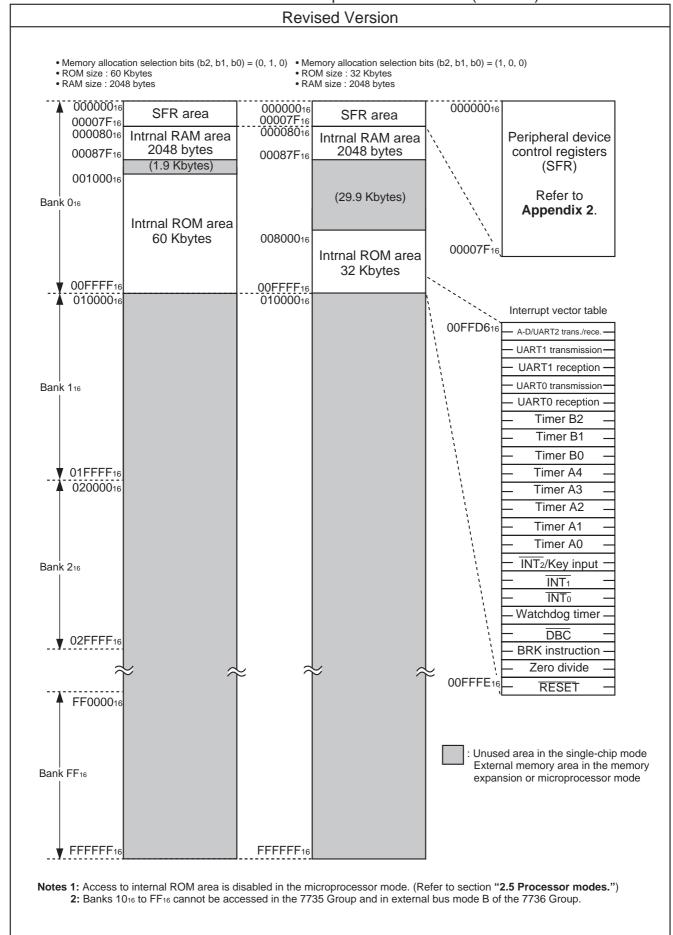

| ☆   | PART 1<br>Page 2-23                         |                                                       |                                                                |             | See pages 2 and 3.                                                             |                         |               |                                                        |                 |

|     | Fig. 2.4.3,<br>PART 1                       |                                                       | (=,                                                            |             | . 3                                                                            |                         |               |                                                        |                 |

|     | Page 21-3                                   |                                                       |                                                                |             |                                                                                |                         |               |                                                        |                 |

|     | Fig. 2,                                     |                                                       |                                                                |             |                                                                                |                         |               |                                                        |                 |

|     | PART 2<br>Page 21-4                         |                                                       |                                                                |             |                                                                                |                         |               |                                                        |                 |

|     | Fig. 2,                                     |                                                       |                                                                |             |                                                                                |                         |               |                                                        |                 |

|     | PART 3<br>Page 20-4                         |                                                       |                                                                |             |                                                                                |                         |               |                                                        |                 |

|     | Fig. 2                                      |                                                       |                                                                |             |                                                                                |                         |               |                                                        |                 |

| ☆   | PART 1<br>Page 19-4                         | Memory allocation selection bits                      |                                                                |             | Memory allo                                                                    | ocation sele            | ection bits   |                                                        |                 |

|     | Table 19.1.3                                | b2 b1                                                 | b0 Programma                                                   | ble area    | b2                                                                             | b1                      | b0            | Programmable                                           | area            |

|     |                                             | 0 0                                                   | 0 01000 <sub>16</sub> –1F                                      |             | 0                                                                              | 0                       | 0             | 01000 <sub>16</sub> –1FFI                              |                 |

|     |                                             | 0 0                                                   | 1 02000 <sub>16</sub> –1F<br>0 08000 <sub>16</sub> –1F         |             | 0                                                                              | 1                       | <u>1</u><br>0 | 02000 <sub>16</sub> –1FFI<br>01000 <sub>16</sub> –0FFI |                 |

|     |                                             | 1 1                                                   | 1 0800016-0F                                                   |             | 1                                                                              | 0                       | 0             | 0800016-0111                                           |                 |

|     |                                             |                                                       |                                                                |             | 1                                                                              | 0                       | 1             | 0C00016-0FF                                            |                 |

|     |                                             |                                                       |                                                                |             | 1                                                                              | 1                       | 0             | 0800016-1FFI                                           | F <sub>16</sub> |

| جاب | PART 1 •••• addresses 00800016 to 00FFFF16. |                                                       |                                                                |             | •••• addre                                                                     | 200 000                 | 00046 to 0    |                                                        |                 |

| ☆   | Page 21-87                                  | addresses 00 <u>8</u>                                 | VOO16 10 00FFFF16.                                             |             | addre                                                                          | 5565 00 <u>0</u>        | UUU16 IU (    | JUITEFF16.                                             |                 |

|     | Line 18                                     |                                                       |                                                                |             |                                                                                |                         |               |                                                        |                 |

|     | Line 18                                     |                                                       |                                                                |             |                                                                                |                         |               |                                                        |                 |

## Revised Points for "7733/7735/7736 Group User's Manual" (REV. A) No. 2

Z

## Revised Points for "7733/7735/7736 Group User's Manual" (REV. A) No. 3

Z