| GRADE | Α |

|-------|---|

# MESC TECHNICAL NEWS No. M7700-62-9912

## Corrections and Supplementary Explanation for "7721 Group User's Manual" (REV. B)

This news includes a few corrections and supplementary explanation for "7721 Group" User's Manual".

And also, this news includes the information previously announced by the MESC TECH-NICAL NEWS (No. M7700-36-9803, Corrections and Supplementary Explanation for "7721 Group User's Manual" REV. A). ★ represents the new information.

The information about the product expansion, electrical characteristics, and development support tools will not be announced by the MESC TECHNICAL NEWS, even if the above information is updated.

So, for the product expansion, electrical characteristics, and development support tools, please refer to the latest version of the following documents in our web site:

- Product Expansion Mitsubishi Microcomputers General Catalog\*

- Electrical Characteristics Datasheets

- Development Support Tools

Datasheets

Microcomputers Development Support Tools Catalog\* Microcomputers Development Support Tools Accessory Guide

#### Please Visit Our Web Site.

- Mitsubishi MCU Technical Information (http://www.infomicom.mesc.co.jp/indexe.htm)

- Mitsubishi Microcomputer Development Support Tools (http://www.tool-spt.mesc.co.jp/index e.htm)

- \* The printed version is also released.

Note: For products not included in the above web site, refer to "1996 MITSUBISHI SEMI-CONDUCTORS DATA BOOK (SINGLE-CHIP 16-BIT MICROCOMPUTERS) Vol. 1 to 2."

Corrections and Supplementary Explanation for "7721 Group User's Manual" (REV. B) No. 1

| ì | Juliections                     | and Supplementary Explanation for "772                                                                                                                                                                        | TOTOUP USELS Maridal (NEV. D) No. 1                                                                                                                                                                                                                                                                              |

|---|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | Page                            | Error                                                                                                                                                                                                         | Correction                                                                                                                                                                                                                                                                                                       |

|   | P2-7<br>(2) Bit 1:<br>Zero Flag | Note: This flag is invalid in the decimal mode addition (the ADC instruction).                                                                                                                                | Note: This flag is invalid in the decimal mode addition (the ADC instruction) and subtraction (the SBC instruction).                                                                                                                                                                                             |

| * | P5-6<br>Last 3 lines            | in order of priority ••• MSB becomes "0." For interrupts not to be accepted, •••                                                                                                                              | in order of priority ••• MSB becomes "0." (When the level sense of an INTi interrupt is used, an interrupt request is not retained. Therefore, if the level at the INTi pin is invalid when the watchdog timer's MSB becomes "0," the interrupt request is not accepted.) For interrupts not to be accepted, ••• |

| * | P7-12<br>Fig. 7.6.1             | (1) Interrupt priotiry detection time select bits  b7 b6 b5 b4 b3 b2 b1 b0 Processor mode register 0 (Address 5E16) Processor mode bits  Clock \( \phi \) 1 output select bit                                 | (1) Interrupt priotiry detection time select bits  b7 b6 b5 b4 b3 b2 b1 b0 Processor mode tegister 0 (Address 5E16) Must be fixed to "0."  Stack bank select bit                                                                                                                                                 |

| * | P8-39                           | <when 16-bit="" a="" as="" modulator="" operating="" pulse="" width=""></when>                                                                                                                                | <when 16-bit="" a="" as="" modulator="" operating="" pulse="" width=""></when>                                                                                                                                                                                                                                   |

|   | Fig. 8.6.1,                     | Bit Functions                                                                                                                                                                                                 | Bit Functions                                                                                                                                                                                                                                                                                                    |

|   | P17-22                          | These bits can be set to "000016" to "FFFE16." Assuming that the set value = n, the "H" level width of the PWM pulse output from the  TAjout pin is expressed as follows: n/fi  (PWM pulse period = n16-1/fi) | These bits can be set to "000016" to "FFFE16." Assuming that the set value = n, the "H" level width of the PWM pulse output from the  TAjout pin is expressed as follows: $\frac{n}{f_i}$ (PWM pulse period = $\frac{2^{16}-1}{f_i}$ )                                                                           |

| * | P8-43<br>Last 2 lines           | the TAjout pin outputs "L" level which has the same width as "H" level width of the PWM pulse, which was set. •••                                                                                             | the TAjou⊤ pin outputs "L" level for a period of (1/fi) X. (m+1) X (n+1). ••••                                                                                                                                                                                                                                   |

| * | P8-45<br>Fig. 8.6.6             | ① Count source                                                                                                                                                                                                | ① Count source                                                                                                                                                                                                                                                                                                   |

|   |                                 | TAjin pin's — input signal ▼                                                                                                                                                                                  | TAjın pin's — input signal ▼                                                                                                                                                                                                                                                                                     |

|   |                                 | ② 8-bit prescaller's underflow signal                                                                                                                                                                         | 8-bit prescaller's underflow signal                                                                                                                                                                                                                                                                              |

|   |                                 | PWM pulse output<br>from TAjoυτ pin                                                                                                                                                                           | PWM pulse output from TAjoυτ pin                                                                                                                                                                                                                                                                                 |

|   |                                 | Timer Aj interrupt request bit                                                                                                                                                                                | Timer Aj interrupt request bit                                                                                                                                                                                                                                                                                   |

| I |                                 |                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                  |

### Corrections and Supplementary Explanation for "7721 Group User's Manual" (REV. B) No. 2

| ì | 301100010110                                                             | and Supplementary Explanation for 112                                                                                                                                                                                                                                                                                                                                                                    | Toroup over a manage (NEV. B) No. 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | Page                                                                     | Error                                                                                                                                                                                                                                                                                                                                                                                                    | Correction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| * | P11-21<br>Line 4,<br>P11-27<br>Lines 3 and 4,<br>P11-38<br>Lines 3 and 4 | ••• after 1 cycle of the transfer clock has passed. •••                                                                                                                                                                                                                                                                                                                                                  | ••• after a maximum of 1 cycle of the transfer clock has passed. •••                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|   | P13-20<br>Table 13.3.3                                                   | Burst transfer mode  Level Sense  O'H"-level input to the DMAREQi pin Change of the TC pin's input level from "H" to "L" (when the TC pin is valid) A write of "0" to the DMAi request bit A write of "0" to the DMAi enable bit  Note: While the DMAi enable bit is "0,"                                                                                                                                | Burst transfer mode  Level Sense                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|   | P13-27<br>Table 13.3.5                                                   | DMAi request bit 0                                                                                                                                                                                                                                                                                                                                                                                       | DMAi request bit  When edge sense is selected in the burst transfer mode: 0  When level sense is selected in the burst transfer mode: not changed  In the cycle-steal transfer mode: 0                                                                                                                                                                                                                                                                                                                                                                           |

| * | P13-28<br>13.3.6 (1)                                                     | (1) Restarting the same DMA ••• beginning At normal and forced termination, the latches of SARi, DARi, and TCRi maintain their values written before the transfer start. (Refer to "Figure 13.3.4-a.") ••• the following procedures:  In single or repeat transfer mode Set the DMAi enable bit to "1." ••• (Refer to "Figure 13.3.4-b.") In array chain ••• mode Re-set the values ••• Set the DMAi ••• | (1) Restarting the same DMA ••• beginning  In single or repeat transfer mode At normal and forced termination, the latches of SARi, DARi, and TCRi maintain their values written before the transfer start. (Refer to "Figure 13.3.4-a.") ••• the following procedures: Set the DMAi enable bit to "1." ••• (Refer to "Figure 13.3.4-b.") In array chain ••• mode As values other than the initial values of SARi and TCRi have been set in their latches (refer to "Table 13.2.5"), it is necessary to re-set them.  ① Re-set the values ••• ② Set the DMAi ••• |

|   | P13-48<br>Line 23                                                        | ••• pin's input level = "L," the DMAi request bit is <u>cleared</u> to "0"; when this pin's input level = "L," the DMAi request bit is <u>set to "1."</u>                                                                                                                                                                                                                                                | ••• pin's input level = "L," the DMAi request bit is set to "1"; when this pin's input level = "H," the DMAi request bit is cleared to "0."                                                                                                                                                                                                                                                                                                                                                                                                                      |

|   | P13-51<br>Fig. 13.4.11                                                   | DMAi enable bit                                                                                                                                                                                                                                                                                                                                                                                          | DMAi enable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

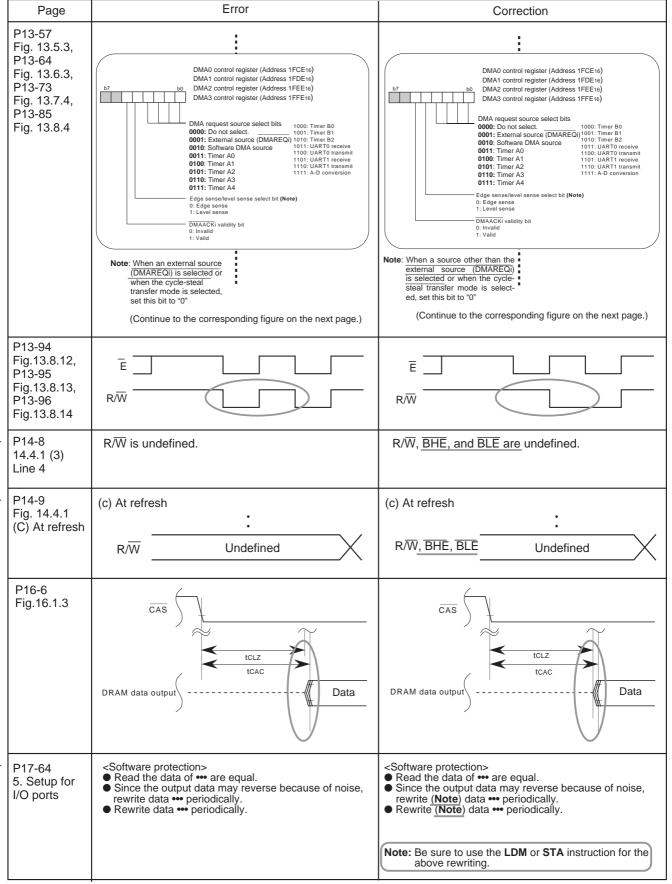

#### Corrections and Supplementary Explanation for "7721 Group User's Manual" (REV. B) No. 3